6.1 ভূমিকা

আধুনিক সাধারণ-উদ্দেশ্যের কম্পিউটার দুটি ধরনের: CISC এবং RISC। CISC এর পূর্ণরূপ হল Complex Instruction Set Computer. RISK এর পূর্ণরূপ হল রিডুসড ইনস্ট্রাকশন সেট কম্পিউটার। 6502 বা 6510 মাইক্রোপ্রসেসর, কমোডোর-64 কম্পিউটারের ক্ষেত্রে প্রযোজ্য, একটি CISC আর্কিটেকচারের চেয়ে RISC আর্কিটেকচারের সাথে বেশি সাদৃশ্যপূর্ণ।

CISC কম্পিউটারের তুলনায় RISC কম্পিউটারে সাধারণত সংক্ষিপ্ত সমাবেশ ভাষা নির্দেশাবলী (বাইটের সংখ্যা অনুসারে) থাকে।

বিঃদ্রঃ : CISC, RISC, বা পুরানো কম্পিউটারের সাথে ডিল করা হোক না কেন, একটি পেরিফেরাল একটি অভ্যন্তরীণ পোর্ট থেকে শুরু হয় এবং কম্পিউটারের সিস্টেম ইউনিটের (বেস ইউনিট) উল্লম্ব পৃষ্ঠের একটি বহিরাগত পোর্টের মাধ্যমে এবং বাহ্যিক ডিভাইসে যায়৷

একটি CISC কম্পিউটারের একটি সাধারণ নির্দেশ দেখা যেতে পারে যেমন একাধিক সংক্ষিপ্ত অ্যাসেম্বলি ল্যাঙ্গুয়েজ নির্দেশকে একটি দীর্ঘ অ্যাসেম্বলি ল্যাঙ্গুয়েজ ইন্সট্রাকশনের সাথে যুক্ত করা যা ফলাফলের নির্দেশকে জটিল করে তোলে। বিশেষ করে, একটি CISC কম্পিউটার মাইক্রোপ্রসেসর রেজিস্টারে মেমরি থেকে অপারেন্ডগুলি লোড করে, একটি অপারেশন করে এবং তারপর ফলাফলটি মেমরিতে আবার সংরক্ষণ করে, সবই এক নির্দেশে। অন্যদিকে, এটি RISC কম্পিউটারের জন্য কমপক্ষে তিনটি নির্দেশ (সংক্ষিপ্ত)।

সিআইএসসি কম্পিউটারের দুটি জনপ্রিয় সিরিজ রয়েছে: ইন্টেল মাইক্রোপ্রসেসর কম্পিউটার এবং এএমডি মাইক্রোপ্রসেসর কম্পিউটার। এএমডি মানে অ্যাডভান্সড মাইক্রো ডিভাইস; এটি একটি সেমিকন্ডাক্টর উৎপাদনকারী কোম্পানি। ইন্টেল মাইক্রোপ্রসেসর সিরিজ, বিকাশের ক্রম অনুসারে, হল 8086, 8088, 80186, 80286, 80386, 80486, পেন্টিয়াম, কোর, আই সিরিজ, সেলেরন এবং জেওন। 8086 এবং 8088 এর মতো প্রাথমিক ইন্টেল মাইক্রোপ্রসেসরগুলির জন্য অ্যাসেম্বলি ভাষার নির্দেশাবলী খুব জটিল নয়। যাইহোক, তারা নতুন মাইক্রোপ্রসেসরের জন্য জটিল। CISC সিরিজের সাম্প্রতিক AMD মাইক্রোপ্রসেসরগুলি হল Ryzen, Opteron, Athlon, Turion, Phenom, এবং Sempron. ইন্টেল এবং এএমডি মাইক্রোপ্রসেসর x86 মাইক্রোপ্রসেসর হিসাবে পরিচিত।

ARM এর অর্থ হল Advanced RISC Machine। এআরএম আর্কিটেকচারগুলি RISC প্রসেসরের একটি পরিবারকে সংজ্ঞায়িত করে যা বিভিন্ন ধরণের অ্যাপ্লিকেশনে ব্যবহারের জন্য উপযুক্ত। ডেস্কটপ পার্সোনাল কম্পিউটারে অনেক ইন্টেল এবং এএমডি মাইক্রোপ্রসেসর ব্যবহার করা হলেও, অনেক এআরএম প্রসেসর নিরাপত্তা-গুরুত্বপূর্ণ সিস্টেম যেমন স্বয়ংচালিত অ্যান্টি-লক ব্রেক এবং স্মার্টওয়াচ, পোর্টেবল ফোন, ট্যাবলেট এবং ল্যাপটপ কম্পিউটারে সাধারণ-উদ্দেশ্য প্রসেসর হিসেবে কাজ করে। . যদিও ছোট এবং বড় উভয় ধরনের মাইক্রোপ্রসেসর দেখা যায়, তবে RISC মাইক্রোপ্রসেসরগুলি বড় ডিভাইসের তুলনায় ছোট ডিভাইসে বেশি পাওয়া যায়।

কম্পিউটার শব্দ

যদি একটি কম্পিউটারকে 32 বিট শব্দের একটি কম্পিউটার বলা হয়, তাহলে এর অর্থ হল মাদারবোর্ডের ভিতরের অংশে বত্রিশ-বিট বাইনারি কোড আকারে তথ্য সংরক্ষণ, স্থানান্তর এবং ম্যানিপুলেট করা হয়। এর মানে হল কম্পিউটারের মাইক্রোপ্রসেসরে সাধারণ-উদ্দেশ্য রেজিস্টারগুলি 32-বিট প্রশস্ত। 6502 মাইক্রোপ্রসেসরের A, X এবং Y রেজিস্টার হল সাধারণ উদ্দেশ্যের রেজিস্টার। তারা আট-বিট প্রশস্ত, এবং তাই কমডোর-64 কম্পিউটার একটি আট-বিট শব্দের কম্পিউটার।

কিছু শব্দভান্ডার

X86 কম্পিউটার

x86 কম্পিউটারের জন্য বাইট, শব্দ, ডাবলওয়ার্ড, কোয়াডওয়ার্ড এবং ডাবল-কোয়াডওয়ার্ডের অর্থ নিম্নরূপ:

- বাইট : 8 বিট

- শব্দ : 16 বিট

- দ্বিগুণ শব্দ : 32 বিট

- কোয়াডওয়ার্ড : 64 বিট

- ডাবল কোয়াডওয়ার্ড : 128 বিট

এআরএম কম্পিউটার

এআরএম কম্পিউটারের জন্য বাইট, হাফওয়ার্ড, ওয়ার্ড এবং ডাবলওয়ার্ডের অর্থ নিম্নরূপ:

- বাইট : 8 বিট

- অর্ধেক হয়ে যান : 16 বিট

- শব্দ : 32 বিট

- দ্বিগুণ শব্দ : 64 বিট

x86 এবং ARM নামের (এবং মান) জন্য পার্থক্য এবং মিল লক্ষ করা উচিত।

বিঃদ্রঃ : উভয় কম্পিউটার প্রকারের সাইন পূর্ণসংখ্যা দুটির পরিপূরক।

মেমরি অবস্থান

কমডোর-64 কম্পিউটারের সাথে, একটি মেমরি অবস্থান সাধারণত এক বাইট হয় কিন্তু পয়েন্টার (পরোক্ষ ঠিকানা) বিবেচনা করার সময় মাঝে মাঝে পরপর দুটি বাইট হতে পারে। একটি আধুনিক x86 কম্পিউটারের সাথে, 16 বাইট (128 বিট) এর একটি ডাবল কোয়াডওয়ার্ডের সাথে ডিল করার সময় একটি মেমরি অবস্থান হল 16 টানা বাইট, 8 বাইট (64 বিট) এর কোয়াডওয়ার্ডের সাথে ডিল করার সময় 8 টানা বাইট, ডাবলওয়ার্ডের সাথে ডিল করার সময় 4 টানা বাইট 4 বাইট (32 বিট), 2 বাইট (16 বিট) এর একটি শব্দ নিয়ে কাজ করার সময় 2 টানা বাইট এবং একটি বাইট (8 বিট) নিয়ে কাজ করার সময় 1 বাইট। একটি আধুনিক এআরএম কম্পিউটারের সাথে, একটি মেমরি অবস্থান 8 বাইট (64 বিট) এর ডাবলওয়ার্ডের সাথে কাজ করার সময় পরপর 8 বাইট, 4 বাইট (32 বিট) এর একটি শব্দের সাথে ডিল করার সময় 4 টানা বাইট, একটি হাফওয়ার্ডের সাথে ডিল করার সময় পরপর 2 বাইট। 2 বাইট (16 বিট), এবং একটি বাইট (8 বিট) নিয়ে কাজ করার সময় 1 বাইট।

এই অধ্যায়টি CISC এবং RISC আর্কিটেকচারে কী সাধারণ এবং তাদের পার্থক্যগুলি কী তা ব্যাখ্যা করে৷ এটি 6502 µP এবং কমোডোর-64 কম্পিউটারের সাথে তুলনা করে করা হয় যেখানে এটি প্রযোজ্য।

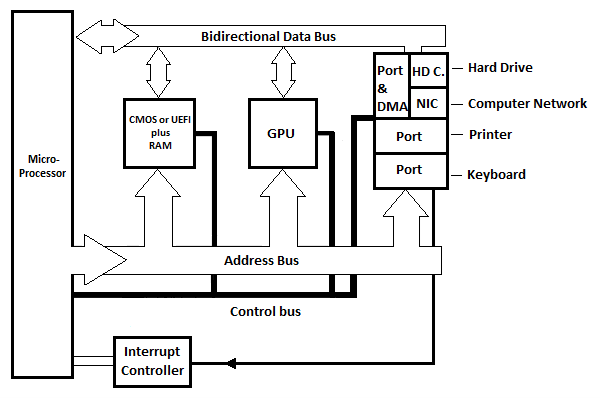

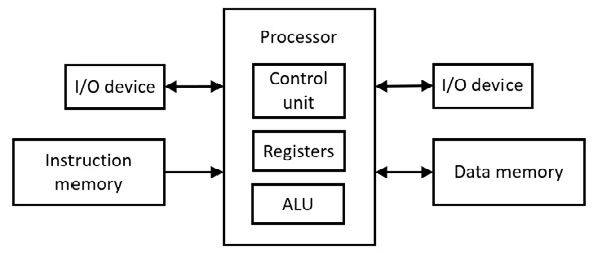

6.2 আধুনিক পিসির মাদারবোর্ড ব্লক ডায়াগ্রাম

পিসি মানে পার্সোনাল কম্পিউটার। একটি ব্যক্তিগত কম্পিউটারের জন্য একটি একক মাইক্রোপ্রসেসর সহ আধুনিক মাদারবোর্ডের জন্য নিম্নলিখিত একটি সাধারণ মৌলিক ব্লক ডায়াগ্রাম। এটি একটি CISC বা RISC মাদারবোর্ডের প্রতিনিধিত্ব করে।

চিত্র 6.21 আধুনিক পিসির বেসিক মাদারবোর্ড ব্লক ডায়াগ্রাম

ডায়াগ্রামে তিনটি অভ্যন্তরীণ পোর্ট দেখানো হয়েছে, তবে অনুশীলনে আরও রয়েছে। প্রতিটি পোর্টের একটি রেজিস্টার রয়েছে যা পোর্ট নিজেই হিসাবে দেখা যায়। প্রতিটি পোর্ট সার্কিটে কমপক্ষে আরেকটি রেজিস্টার থাকে যাকে 'স্ট্যাটাস রেজিস্টার' বলা যেতে পারে। স্ট্যাটাস রেজিস্টার সেই প্রোগ্রামের পোর্টকে নির্দেশ করে যা মাইক্রোপ্রসেসরে ইন্টারাপ্ট সিগন্যাল পাঠাচ্ছে। একটি ইন্টারাপ্ট কন্ট্রোলার সার্কিট রয়েছে (দেখানো হয়নি) যা বিভিন্ন পোর্ট থেকে বিভিন্ন ইন্টারাপ্ট লাইনের মধ্যে পার্থক্য করে এবং µP-তে মাত্র কয়েকটি লাইন রয়েছে।

ডায়াগ্রামে HD.C মানে হার্ড ড্রাইভ কার্ড। NIC মানে নেটওয়ার্ক ইন্টারফেস কার্ড। হার্ড ড্রাইভ কার্ড (সার্কিট) হার্ড ড্রাইভের সাথে সংযুক্ত যা আধুনিক কম্পিউটারের বেস ইউনিট (সিস্টেম ইউনিট) এর ভিতরে রয়েছে। নেটওয়ার্ক ইন্টারফেস কার্ড (সার্কিট) একটি বাহ্যিক তারের মাধ্যমে অন্য কম্পিউটারে সংযুক্ত করা হয়। ডায়াগ্রামে, একটি পোর্ট এবং একটি DMA (নিম্নলিখিত চিত্রটি পড়ুন) যা হার্ড ডিস্ক কার্ড এবং/অথবা নেটওয়ার্ক ইন্টারফেস কার্ডের সাথে সংযুক্ত। ডিএমএ মানে ডাইরেক্ট মেমরি অ্যাক্সেস।

কমোডোর-64 কম্পিউটার অধ্যায় থেকে মনে রাখবেন যে মেমরি থেকে বাইটগুলি ডিস্ক ড্রাইভ বা অন্য কম্পিউটারে পাঠানোর জন্য, প্রতিটি বাইটকে সংশ্লিষ্ট অভ্যন্তরীণ পোর্টে অনুলিপি করার আগে মাইক্রোপ্রসেসরের একটি রেজিস্টারে অনুলিপি করতে হবে এবং তারপরে স্বয়ংক্রিয়ভাবে ডিভাইসে। মেমরিতে ডিস্ক ড্রাইভ বা অন্য কম্পিউটার থেকে বাইটগুলি গ্রহণ করার জন্য, মেমরিতে অনুলিপি করার আগে প্রতিটি বাইট সংশ্লিষ্ট অভ্যন্তরীণ পোর্ট রেজিস্টার থেকে একটি মাইক্রোপ্রসেসর রেজিস্টারে অনুলিপি করতে হবে। স্ট্রীমের বাইটের সংখ্যা বেশি হলে এটি সাধারণত দীর্ঘ সময় নেয়। দ্রুত স্থানান্তরের সমাধান হল মাইক্রোপ্রসেসরের মধ্য দিয়ে না গিয়ে সরাসরি মেমরি অ্যাক্সেস (সার্কিট) ব্যবহার করা।

ডিএমএ সার্কিটটি পোর্ট এবং এইচডি এর মধ্যে রয়েছে। সি বা এনআইসি। ডিএমএ সার্কিটের সরাসরি মেমরি অ্যাক্সেসের সাথে, মাইক্রোপ্রসেসরের ক্রমাগত অংশগ্রহণ ছাড়াই ডিএমএ সার্কিট এবং মেমরি (র্যাম) এর মধ্যে বাইটের বড় স্ট্রিমের স্থানান্তর সরাসরি হয়। DMA µP এর জায়গায় ঠিকানা বাস এবং ডেটা বাস ব্যবহার করে। স্থানান্তরের মোট সময়কাল µP হার্ড ব্যবহার করার চেয়ে কম। এইচডি সি বা এনআইসি উভয়ই ডিএমএ ব্যবহার করে যখন তাদের কাছে RAM (মেমরি) দিয়ে স্থানান্তরের জন্য ডেটার (বাইট) একটি বড় প্রবাহ থাকে।

GPU মানে গ্রাফিক্স প্রসেসিং ইউনিট। মাদারবোর্ডের এই ব্লকটি স্ক্রিনে পাঠ্য এবং চলমান বা স্থির চিত্র পাঠানোর জন্য দায়ী।

আধুনিক কম্পিউটারের সাথে (পিসি), কোন রিড অনলি মেমরি (রম) নেই। তবে BIOS বা UEFI আছে যা এক ধরনের অ-উদ্বায়ী RAM। BIOS-এর তথ্য আসলে একটি ব্যাটারি দ্বারা রক্ষণাবেক্ষণ করা হয়। ব্যাটারি হল যা আসলে ঘড়ির টাইমারটিকে কম্পিউটারের জন্য সঠিক সময় এবং তারিখে বজায় রাখে। UEFI BIOS এর পরে উদ্ভাবিত হয়েছিল, এবং BIOS প্রতিস্থাপন করেছে যদিও BIOS এখনও আধুনিক পিসিগুলিতে বেশ প্রাসঙ্গিক। আমরা পরে এই বিষয়ে আরও আলোচনা করব!

আধুনিক পিসিতে, µP এবং অভ্যন্তরীণ পোর্ট সার্কিট (এবং মেমরি) এর মধ্যে ঠিকানা এবং ডেটা বাসগুলি সমান্তরাল বাস নয়। এগুলি সিরিয়াল বাস যেগুলির একটি দিক থেকে সংক্রমণের জন্য দুটি কন্ডাক্টর এবং বিপরীত দিকে সংক্রমণের জন্য অন্য দুটি কন্ডাক্টর প্রয়োজন। এর মানে, উদাহরণস্বরূপ, যে 32-বিটগুলি সিরিজে (একের পর এক বিট) উভয় দিকে পাঠানো যেতে পারে।

যদি সিরিয়াল ট্রান্সমিশন দুটি কন্ডাক্টর (দুটি লাইন) সহ শুধুমাত্র এক দিকে হয়, তাহলে তাকে অর্ধ-দ্বৈত বলা হয়। যদি সিরিয়াল ট্রান্সমিশনটি চারটি কন্ডাক্টর সহ উভয় দিকে থাকে, উভয় দিকে একটি জোড়া থাকে, যাকে ফুল-ডুপ্লেক্স বলা হয়।

আধুনিক কম্পিউটারের পুরো মেমরিতে এখনও বাইট অবস্থানের একটি সিরিজ রয়েছে: প্রতি বাইট আট-বিট। একটি আধুনিক কম্পিউটারের মেমরি স্পেস কমপক্ষে 4 গিগা বাইট = 4 x 210 x 2 10 x 2 10 = 4 x 1,073,741,824 10 বাইট = 4 x 1024 10 x 1024 10 x 1024 10 = 4 x 1,073,741,824 10 .

বিঃদ্রঃ : যদিও আগের মাদারবোর্ডে কোনো টাইমার সার্কিট দেখানো হয়নি, তবে সব আধুনিক মাদারবোর্ডেই টাইমার সার্কিট রয়েছে।

6.3 x64 কম্পিউটার আর্কিটেকচার বেসিক

6.31 x64 রেজিস্টার সেট

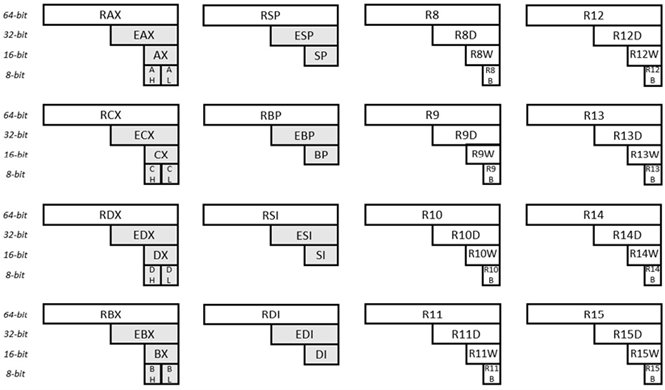

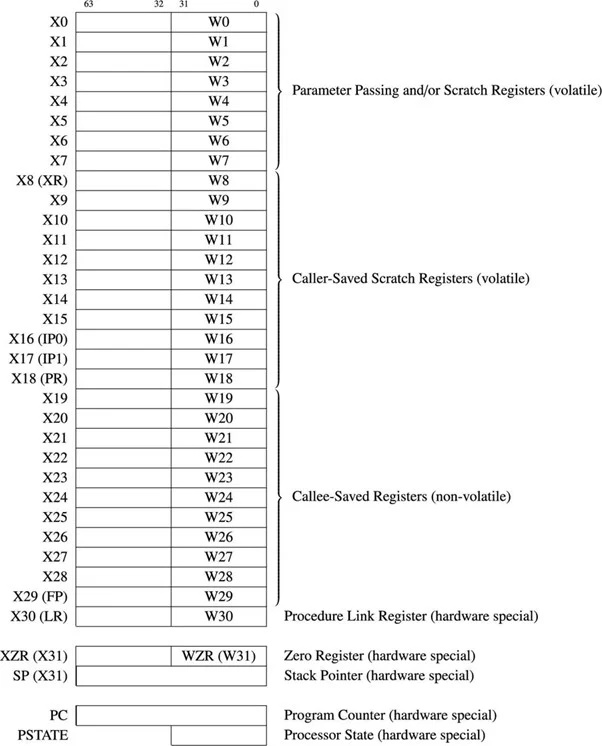

মাইক্রোপ্রসেসরের x86 সিরিজের 64-বিট মাইক্রোপ্রসেসর একটি 64-বিট মাইক্রোপ্রসেসর। একই সিরিজের 32-বিট প্রসেসর প্রতিস্থাপন করা বেশ আধুনিক। 64-বিট মাইক্রোপ্রসেসরের সাধারণ উদ্দেশ্য রেজিস্টার এবং তাদের নাম নিম্নরূপ:

চিত্র 6.31 x64 এর জন্য সাধারণ উদ্দেশ্য রেজিস্টার

ষোলটি (16) সাধারণ উদ্দেশ্য রেজিস্টার প্রদত্ত চিত্রে দেখানো হয়েছে। এই রেজিস্টারগুলির প্রতিটি 64-বিট প্রশস্ত। উপরের বাম কোণে রেজিস্টারের দিকে তাকালে, 64 বিটগুলিকে RAX হিসাবে চিহ্নিত করা হয়। এই একই রেজিস্টারের প্রথম 32 বিট (ডান দিক থেকে) EAX হিসাবে চিহ্নিত করা হয়। এই একই রেজিস্টারের প্রথম 16 বিট (ডান দিক থেকে) AX হিসাবে চিহ্নিত করা হয়। এই একই রেজিস্টারের দ্বিতীয় বাইট (ডান দিক থেকে) AH হিসাবে চিহ্নিত করা হয়েছে (এখানে H মানে উচ্চ)। এবং প্রথম বাইট (এই একই রেজিস্টারের) AL হিসাবে চিহ্নিত করা হয়েছে (এখানে L মানে কম)। নীচে-ডান কোণে রেজিস্টারের দিকে তাকালে, 64 বিটগুলিকে R15 হিসাবে চিহ্নিত করা হয়েছে। এই একই রেজিস্টারের প্রথম 32 বিট R15D হিসাবে চিহ্নিত করা হয়। এই একই রেজিস্টারের প্রথম 16 বিট R15W হিসাবে চিহ্নিত করা হয়। এবং প্রথম বাইট R15B হিসাবে চিহ্নিত করা হয়। অন্যান্য রেজিস্টারের নাম (এবং সাব-রেজিস্টার) একইভাবে ব্যাখ্যা করা হয়েছে।

ইন্টেল এবং AMD µPs এর মধ্যে কিছু পার্থক্য রয়েছে। এই বিভাগে তথ্য ইন্টেলের জন্য।

6502 µP এর সাথে, প্রোগ্রাম কাউন্টার রেজিস্টার (সরাসরি অ্যাক্সেসযোগ্য নয়) যা কার্যকর করার পরবর্তী নির্দেশ ধারণ করে 16-বিট প্রশস্ত। এখানে (x64), প্রোগ্রাম কাউন্টারটিকে নির্দেশ নির্দেশক বলা হয় এবং এটি 64-বিট প্রশস্ত। এটি RIP হিসাবে লেবেল করা হয়। এর মানে হল যে x64 µP 264 = 1.844674407 x 1019 (আসলে 18,446,744,073,709,551,616) মেমরি বাইট অবস্থান পর্যন্ত ঠিকানা দিতে পারে। RIP একটি সাধারণ-উদ্দেশ্য রেজিস্টার নয়।

স্ট্যাক পয়েন্টার রেজিস্টার বা আরএসপি 16টি সাধারণ উদ্দেশ্য রেজিস্টারের মধ্যে রয়েছে। এটি মেমরিতে শেষ স্ট্যাক এন্ট্রি নির্দেশ করে। 6502 µP এর মত, x64 এর স্ট্যাক নিচের দিকে বৃদ্ধি পায়। x64 এর সাথে, RAM-এর স্ট্যাকটি সাবরুটিনের জন্য রিটার্ন ঠিকানা সংরক্ষণ করতে ব্যবহৃত হয়। এটি 'ছায়া স্থান' সংরক্ষণের জন্যও ব্যবহৃত হয় (নিম্নলিখিত আলোচনা পড়ুন)।

6502 µP এর একটি 8-বিট প্রসেসর স্ট্যাটাস রেজিস্টার রয়েছে। x64 এর সমতুল্যকে RFLAGS রেজিস্টার বলা হয়। এই রেজিস্টার ফ্ল্যাগগুলি সঞ্চয় করে যা অপারেশনের ফলাফলের জন্য এবং প্রসেসর (µP) নিয়ন্ত্রণের জন্য ব্যবহৃত হয়। এটি 64-বিট প্রশস্ত। উচ্চতর 32 বিট সংরক্ষিত এবং বর্তমানে ব্যবহার করা হয় না। নিম্নলিখিত টেবিলটি RFLAGS রেজিস্টারে সাধারণত ব্যবহৃত বিটগুলির নাম, সূচক এবং অর্থ দেয়:

| সারণি 6.31.1 সর্বাধিক ব্যবহৃত RFLAGS পতাকা (বিট) |

|||

|---|---|---|---|

| প্রতীক | বিট | নাম | উদ্দেশ্য |

| সিএফ | 0 | বহন | এটি সেট করা হয় যদি একটি গাণিতিক অপারেশন ফলাফলের সবচেয়ে উল্লেখযোগ্য বিট থেকে একটি বহন বা ধার তৈরি করে; অন্যথায় সাফ করা হয়েছে। এই পতাকা স্বাক্ষরবিহীন-পূর্ণসংখ্যার পাটিগণিতের জন্য একটি ওভারফ্লো অবস্থা নির্দেশ করে। এটি একাধিক-নির্ভুল পাটিগণিতেও ব্যবহৃত হয়। |

| পিএফ | 2 | সমতা | এটি সেট করা হয় যদি ফলাফলের সর্বনিম্ন-গুরুত্বপূর্ণ বাইটটিতে 1 বিটের একটি জোড় সংখ্যা থাকে; অন্যথায় সাফ করা হয়েছে। |

| অফ | 4 | সামঞ্জস্য করুন | এটি সেট করা হয় যদি একটি গাণিতিক অপারেশন ফলাফলের বিট 3 থেকে একটি বহন বা ধার তৈরি করে; অন্যথায় সাফ করা হয়েছে। এই পতাকাটি বাইনারি-কোডেড দশমিক (BCD) পাটিগণিতে ব্যবহৃত হয়। |

| জেডএফ | 6 | শূন্য | ফলাফল শূন্য হলে এটি সেট করা হয়; অন্যথায় সাফ করা হয়েছে। |

| এসএফ | 7 | চিহ্ন | এটি সেট করা হয় যদি এটি ফলাফলের সবচেয়ে-গুরুত্বপূর্ণ বিটের সমান হয় যা একটি স্বাক্ষরিত পূর্ণসংখ্যার চিহ্ন বিট (0 একটি ধনাত্মক মান নির্দেশ করে এবং 1 একটি ঋণাত্মক মান নির্দেশ করে)। |

| অফ | এগারো | উপচে পড়া | এটি সেট করা হয় যদি পূর্ণসংখ্যার ফলাফলটি খুব বড় একটি ধনাত্মক সংখ্যা বা খুব ছোট একটি ঋণাত্মক সংখ্যা (সাইন-বিট ব্যতীত) গন্তব্য অপারেন্ডে ফিট করা যায়; অন্যথায় সাফ করা হয়েছে। এই পতাকাটি স্বাক্ষরিত পূর্ণসংখ্যা (দুই এর পরিপূরক) পাটিগণিতের জন্য একটি ওভারফ্লো অবস্থা নির্দেশ করে। |

| ডিএফ | 10 | অভিমুখ | এটি সেট করা হয় যদি দিক স্ট্রিং নির্দেশাবলী কাজ করে (বৃদ্ধি বা হ্রাস)। |

| আইডি | একুশ | শনাক্তকরণ | এটি সেট করা হয় যদি এটি পরিবর্তনযোগ্যতা CPUID নির্দেশের উপস্থিতি নির্দেশ করে। |

পূর্বে নির্দেশিত আঠারোটি 64-বিট রেজিস্টার ছাড়াও, x64 আর্কিটেকচার µP-এ ফ্লোটিং পয়েন্ট পাটিগণিতের জন্য আটটি 80-বিট প্রশস্ত রেজিস্টার রয়েছে। এই আটটি রেজিস্টার এমএমএক্স রেজিস্টার হিসাবেও ব্যবহার করা যেতে পারে (নিচের আলোচনা পড়ুন)। এছাড়াও XMM এর জন্য 128-বিট রেজিস্টার রয়েছে (নিম্নলিখিত আলোচনা পড়ুন)।

যে নিবন্ধন সম্পর্কে সব না. আরও x64 রেজিস্টার রয়েছে যা সেগমেন্ট রেজিস্টার (বেশিরভাগই x64 তে অব্যবহৃত), কন্ট্রোল রেজিস্টার, মেমরি ম্যানেজমেন্ট রেজিস্টার, ডিবাগ রেজিস্টার, ভার্চুয়ালাইজেশন রেজিস্টার, পারফরম্যান্স রেজিস্টার যা সমস্ত ধরণের অভ্যন্তরীণ প্যারামিটার ট্র্যাক করে (ক্যাশে হিট/মিস, মাইক্রো-অপস এক্সিকিউটেড, টাইমিং) , এবং আরো অনেক কিছু).

SIMD

SIMD মানে একক নির্দেশ মাল্টিপল ডেটা। এর মানে হল যে একটি অ্যাসেম্বলি ভাষার নির্দেশনা একটি মাইক্রোপ্রসেসরে একই সময়ে একাধিক ডেটাতে কাজ করতে পারে। নিম্নলিখিত টেবিল বিবেচনা করুন:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | এগারো | 12 | 13 | 14 | পনের | 16 |

| = | 10 | 12 | 14 | 16 | 18 | বিশ | 22 | 24 |

এই সারণীতে, আট জোড়া সংখ্যা সমান্তরালভাবে যোগ করা হয়েছে (একই সময়কালে) আটটি উত্তর দেওয়ার জন্য। একটি সমাবেশ ভাষার নির্দেশনা MMX রেজিস্টারে আটটি সমান্তরাল পূর্ণসংখ্যা সংযোজন করতে পারে। XMM রেজিস্টারগুলির সাথে একই জিনিস করা যেতে পারে। সুতরাং, পূর্ণসংখ্যার জন্য MMX নির্দেশাবলী এবং ফ্লোটের জন্য XMM নির্দেশাবলী রয়েছে।

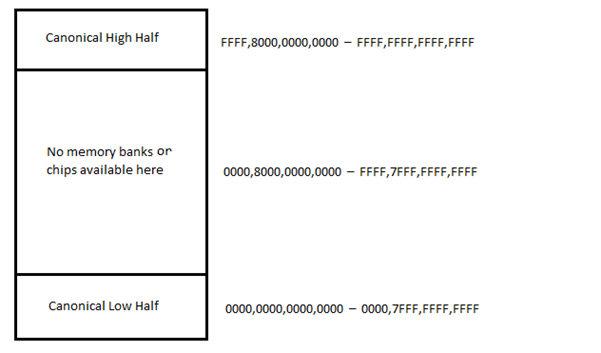

6.32 মেমরি ম্যাপ এবং x64

ইন্সট্রাকশন পয়েন্টার (প্রোগ্রাম কাউন্টার) 64 বিট সহ, এর মানে হল 264 = 1.844674407 x 1019 মেমরি বাইট অবস্থানগুলিকে সম্বোধন করা যেতে পারে। হেক্সাডেসিমেলে, সর্বোচ্চ বাইট অবস্থান হল FFFF, FFFF, FFFF, FFFF16। আজকের কোনো সাধারণ কম্পিউটার এত বড় মেমরি (সম্পূর্ণ) জায়গা দিতে পারে না। সুতরাং, x64 কম্পিউটারের জন্য একটি উপযুক্ত মেমরি মানচিত্র নিম্নরূপ:

লক্ষ্য করুন যে 0000,8000,0000,000016 থেকে FFFF, 7FFF, FFFF, FFFF16 পর্যন্ত কোনও মেমরি অবস্থান নেই (কোনও মেমরি র্যাম ব্যাঙ্ক নেই)। এটি FFFF,0000,0000,000116 এর একটি পার্থক্য যা বেশ বড়। ক্যানোনিকাল উচ্চ অর্ধেক অপারেটিং সিস্টেম আছে, যখন ক্যানোনিকাল নিম্ন অর্ধেক ব্যবহারকারী প্রোগ্রাম (অ্যাপ্লিকেশন) এবং ডেটা আছে। অপারেটিং সিস্টেম দুটি অংশ নিয়ে গঠিত: একটি ছোট UEFI (BIOS) এবং একটি বড় অংশ যা হার্ড ড্রাইভ থেকে লোড করা হয়। পরবর্তী অধ্যায়ে আধুনিক অপারেটিং সিস্টেম সম্পর্কে আরও আলোচনা করা হয়েছে। এই মেমরি ম্যাপের সাথে এবং কমোডোর-64-এর সাথে সাদৃশ্য লক্ষ্য করুন যখন 64KB অনেক মেমরির মতো দেখাতে পারে।

এই প্রসঙ্গে, অপারেটিং সিস্টেমটিকে মোটামুটিভাবে 'কার্নেল' বলা হয়। কার্নেলটি কমোডোর-64 কম্পিউটারের কার্নালের মতোই, তবে এর অনেক বেশি সাবরুটিন রয়েছে।

x64-এর জন্য endianness হল সামান্য endian, যার মানে হল একটি অবস্থানের জন্য, নিম্ন ঠিকানাটি মেমরির নিম্ন বিষয়বস্তুর বাইটকে নির্দেশ করে।

6.33 x64 এর জন্য অ্যাসেম্বলি ল্যাঙ্গুয়েজ অ্যাড্রেসিং মোড

অ্যাড্রেসিং মোড হল এমন উপায় যা একটি নির্দেশনা µP রেজিস্টার এবং মেমরি (অভ্যন্তরীণ পোর্ট রেজিস্টার সহ) অ্যাক্সেস করতে পারে। x64-এর অনেক অ্যাড্রেসিং মোড আছে, কিন্তু এখানে শুধুমাত্র সাধারণভাবে ব্যবহৃত অ্যাড্রেসিং মোডগুলিকে সম্বোধন করা হয়েছে। এখানে একটি নির্দেশের জন্য সাধারণ সিনট্যাক্স হল:

opcode গন্তব্য, উৎস

দশমিক সংখ্যাগুলো কোনো উপসর্গ বা প্রত্যয় ছাড়াই লেখা হয়। 6502 এর সাথে, উত্সটি অন্তর্নিহিত। x64-এ 6502-এর চেয়ে বেশি অপ-কোড রয়েছে, কিন্তু কিছু অপকোডের একই স্মৃতিবিদ্যা রয়েছে। পৃথক x64 নির্দেশাবলী পরিবর্তনশীল দৈর্ঘ্যের এবং আকার 1 থেকে 15 বাইট পর্যন্ত হতে পারে। সাধারণত ব্যবহৃত অ্যাড্রেসিং মোডগুলি নিম্নরূপ:

অবিলম্বে ঠিকানা মোড

এখানে, উৎস অপারেন্ড একটি প্রকৃত মান এবং একটি ঠিকানা বা লেবেল নয়। উদাহরণ (মন্তব্যটি পড়ুন):

EAX যোগ করুন, 14 ; 64-বিট RAX-এর দশমিক 14 থেকে 32-বিট EAX যোগ করুন, উত্তরটি EAX (গন্তব্য) এ রয়ে গেছে

রেজিস্টার অ্যাড্রেসিং মোডে নিবন্ধন করুন

উদাহরণ:

R8B, AL যোগ করুন; 64-বিট R8-এর R8B-তে RAX-এর 8-বিট AL যোগ করুন – উত্তরগুলি R8B (গন্তব্য)-এ রয়ে গেছে

পরোক্ষ এবং ইন্ডেক্সড অ্যাড্রেসিং মোড

6502 µP সহ পরোক্ষ ঠিকানার অর্থ হল নির্দেশে প্রদত্ত ঠিকানার অবস্থানে চূড়ান্ত অবস্থানের কার্যকর ঠিকানা (পয়েন্টার) রয়েছে। x64 এর সাথে একই জিনিস ঘটে। 6502 µP সহ সূচক ঠিকানার অর্থ হল একটি µP রেজিস্টারের বিষয়বস্তু প্রদত্ত ঠিকানায় যুক্ত করা হয়েছে যাতে কার্যকর ঠিকানা থাকে। x64 এর সাথেও একই রকম ঘটনা ঘটে। এছাড়াও, x64 এর সাথে, প্রদত্ত ঠিকানায় যোগ করার আগে রেজিস্টারের বিষয়বস্তুকে 1 বা 2 বা 4 বা 8 দ্বারা গুণ করা যেতে পারে। x64-এর mov (অনুলিপি) নির্দেশ পরোক্ষ এবং সূচীকৃত ঠিকানা উভয়ই একত্রিত করতে পারে। উদাহরণ:

MOV R8W, 1234[8*RAX+RCX]; ঠিকানায় শব্দ সরান (8 x RAX + RCX) + 1234

এখানে, R8W এর R8 এর প্রথম 16-বিট রয়েছে। প্রদত্ত ঠিকানাটি হল 1234৷ RAX রেজিস্টারে একটি 64-বিট নম্বর রয়েছে যা 8 দ্বারা গুণ করা হয়৷ ফলাফলটি 64-বিট RCX রেজিস্টারের সামগ্রীতে যোগ করা হয়৷ কার্যকর ঠিকানা পেতে এই দ্বিতীয় ফলাফলটি প্রদত্ত ঠিকানায় যোগ করা হয়েছে যা হল 1234। কার্যকর ঠিকানার অবস্থানে থাকা নম্বরটি R8 রেজিস্টারের প্রথম 16-বিট স্থানে (R8W) স্থানান্তরিত (কপি করা হয়েছে) যেখানে যা ছিল তা প্রতিস্থাপন করে। বর্গাকার বন্ধনীর ব্যবহার লক্ষ্য করুন। মনে রাখবেন x64-এ একটি শব্দ 16-বিট প্রশস্ত।

RIP আপেক্ষিক ঠিকানা

6502 µP এর জন্য, আপেক্ষিক ঠিকানা শুধুমাত্র শাখা নির্দেশাবলীর সাথে ব্যবহার করা হয়। সেখানে, অপকোডের একক অপারেন্ড হল একটি অফসেট যা কার্যকর নির্দেশনা ঠিকানার (ডেটা ঠিকানা নয়) জন্য প্রোগ্রাম কাউন্টারের বিষয়বস্তুর সাথে যোগ বা বিয়োগ করা হয়। একই জিনিস x64 এর সাথে ঘটে যেখানে প্রোগ্রাম কাউন্টারকে নির্দেশ পয়েন্টার বলা হয়। x64 এর সাথে নির্দেশনা শুধুমাত্র একটি শাখা নির্দেশ হতে হবে না। RIP- সম্পর্কিত ঠিকানার একটি উদাহরণ হল:

MOV AL, [RIP]

RAX-এর AL-এর একটি 8-বিট স্বাক্ষরিত নম্বর রয়েছে যা পরবর্তী নির্দেশে নির্দেশ করার জন্য RIP (64-বিট ইন্সট্রাকশন পয়েন্টার) এর বিষয়বস্তু থেকে যোগ বা বিয়োগ করা হয়। উল্লেখ্য যে উৎস এবং গন্তব্য এই নির্দেশে ব্যতিক্রমীভাবে অদলবদল করা হয়েছে। এছাড়াও বর্গাকার বন্ধনীর ব্যবহার লক্ষ্য করুন যা RIP এর বিষয়বস্তুকে নির্দেশ করে।

6.34 x64 এর সাধারণভাবে ব্যবহৃত নির্দেশাবলী

নিম্নলিখিত টেবিলে * মানে অপকোডের একটি উপসেটের বিভিন্ন সম্ভাব্য প্রত্যয়:

| সারণি 6.34.1 x64-এ সাধারণভাবে ব্যবহৃত নির্দেশাবলী |

|

|---|---|

| অপকোড | অর্থ |

| MOV | মেমরি এবং রেজিস্টারে/থেকে/এর মধ্যে সরান (কপি) |

| CMOV* | বিভিন্ন শর্তসাপেক্ষ চাল |

| এক্সসিএইচজি | বিনিময় |

| BSWAP | বাইট অদলবদল |

| পুশ/পপ | স্ট্যাক ব্যবহার |

| ADD/ADC | ক্যারি সহ যোগ করুন |

| SUB/SBC | ক্যারি সহ বিয়োগ করুন |

| MUL/IMUL | গুণিত/আনসাইন করা |

| DIV/IDIV | বিভক্ত/স্বাক্ষরবিহীন |

| INC/DEC | ইনক্রিমেন্ট/ডিক্রিমেন্ট |

| NEG | নেগেটিভ |

| সিএমপি | তুলনা করা |

| এবং/অথবা/XOR/না | বিটওয়াইজ অপারেশন |

| SHR/SAR | ডান লজিক্যাল/পাটিগণিত স্থানান্তর করুন |

| SHL/SAL | লজিক্যাল/পাটিগণিত বাম স্থানান্তর করুন |

| ROR/ROLE | ডান/বামে ঘোরান |

| আরসিআর/আরসিএল | ক্যারি বিটের মাধ্যমে ডান/বামে ঘোরান |

| BT/BTS/BTR | বিট পরীক্ষা/এবং সেট/এবং রিসেট |

| জেএমপি | শর্তহীন লাফ |

| JE/JNE/JC/JNC/J* | সমান/সমান না হলে লাফ দিন |

| ওয়াক/ওয়াক/ওয়াক | ECX দিয়ে লুপ করুন |

| কল/RET | সাবরুটিন/রিটার্ন কল করুন |

| NOP | কোন অপারেশন নেই |

| CPUID | CPU তথ্য |

x64-এ গুন এবং ভাগ করার নির্দেশনা রয়েছে। এটির µP তে গুণন এবং ভাগ হার্ডওয়্যার সার্কিট রয়েছে। 6502 µP এর গুণন এবং ভাগ হার্ডওয়্যার সার্কিট নেই। সফ্টওয়্যার (বিট স্থানান্তর সহ) এর চেয়ে হার্ডওয়্যার দ্বারা গুণন এবং ভাগ করা দ্রুত।

স্ট্রিং নির্দেশাবলী

অনেকগুলি স্ট্রিং নির্দেশাবলী রয়েছে, তবে এখানে আলোচনা করা একমাত্র MOVS (মুভ স্ট্রিংয়ের জন্য) নির্দেশনা হল C000 ঠিকানা থেকে শুরু হওয়া একটি স্ট্রিং অনুলিপি করার জন্য এইচ . C100 ঠিকানায় শুরু করতে এইচ , নিম্নলিখিত নির্দেশাবলী ব্যবহার করুন:

MOVS [C100H], [C000H]

হেক্সাডেসিমেলের জন্য H প্রত্যয়টি লক্ষ্য করুন।

6.35 x64 এ লুপিং

6502 µP-এ লুপ করার জন্য শাখা নির্দেশাবলী রয়েছে। একটি শাখার নির্দেশ একটি ঠিকানার অবস্থানে যায় যেখানে নতুন নির্দেশ রয়েছে। ঠিকানার অবস্থানটিকে 'লুপ' বলা যেতে পারে। x64 এ লুপ করার জন্য LOOP/LOOPE/LOOPNE নির্দেশাবলী রয়েছে। এই সংরক্ষিত সমাবেশ ভাষার শব্দগুলিকে 'লুপ' লেবেলের সাথে বিভ্রান্ত করা উচিত নয় (উদ্ধৃতি ব্যতীত)। আচরণটি নিম্নরূপ:

LOOP ECX হ্রাস করে এবং ECX শূন্য না কিনা তা পরীক্ষা করে। যদি সেই শর্ত (শূন্য) পূরণ হয়, এটি একটি নির্দিষ্ট লেবেলে চলে যায়। অন্যথায়, এটি পড়ে যায় (নিম্নলিখিত আলোচনায় বাকি নির্দেশাবলীর সাথে চালিয়ে যান)।

LOOPE ECX কে হ্রাস করে এবং পরীক্ষা করে যে ECX শূন্য নয় (উদাহরণস্বরূপ 1 হতে পারে) এবং ZF সেট করা হয়েছে (1 এ)। যদি এই শর্তগুলি পূরণ করা হয়, এটি লেবেলে লাফ দেয়। অন্যথায়, এটি মাধ্যমে পড়ে.

LOOPNE ECX-কে হ্রাস করে এবং পরীক্ষা করে যে ECX শূন্য নয় এবং ZF সেট করা নেই (অর্থাৎ, শূন্য হবে)। যদি এই শর্তগুলি পূরণ করা হয় তবে এটি লেবেলে চলে যায়। অন্যথায়, এটি মাধ্যমে পড়ে.

x64 এর সাথে, RCX রেজিস্টার বা এর সাব পার্টস যেমন ECX বা CX, কাউন্টার ইন্টিজার ধারণ করে। LOOP নির্দেশাবলীর সাথে, কাউন্টারটি সাধারণত কাউন্ট ডাউন করে, প্রতিটি লাফের (লুপ) জন্য 1 দ্বারা হ্রাস পায়। নিম্নলিখিত লুপিং কোড সেগমেন্টে, EAX রেজিস্টারের সংখ্যা দশটি পুনরাবৃত্তিতে 0 থেকে 10 পর্যন্ত বৃদ্ধি পায় যখন ECX-এ সংখ্যাটি 10 গুণ কমে (মন্তব্যগুলি পড়ুন):

MOV EAX, 0 ;

MOV ECX, 10; ডিফল্টরূপে 10 বার গণনা করুন, প্রতিটি পুনরাবৃত্তির জন্য একবার

লেবেল:

INC EAX; লুপ বডি হিসাবে EAX বৃদ্ধি করুন

লুপ লেবেল; EAX হ্রাস করুন, এবং যদি EAX শূন্য না হয়, তাহলে 'লেবেল:' থেকে লুপ বডি পুনরায় কার্যকর করুন

লুপ কোডিং শুরু হয় 'লেবেল:' থেকে। কোলনের ব্যবহার লক্ষ্য করুন। লুপ কোডিং 'LOOP লেবেল' দিয়ে শেষ হয় যা বলে decrement EAX। যদি এটির বিষয়বস্তু শূন্য না হয়, তাহলে 'লেবেল:' এর পরে নির্দেশে ফিরে যান এবং 'LOOP লেবেল' পর্যন্ত নিচের দিকে আসা যেকোনো নির্দেশ (শরীরের সমস্ত নির্দেশাবলী) পুনরায় কার্যকর করুন৷ মনে রাখবেন যে 'লেবেল' এর এখনও অন্য নাম থাকতে পারে।

6.36 x64 এর ইনপুট/আউটপুট

অধ্যায়ের এই বিভাগটি একটি আউটপুট (অভ্যন্তরীণ) পোর্টে ডেটা প্রেরণ বা একটি ইনপুট (অভ্যন্তরীণ) পোর্ট থেকে ডেটা গ্রহণের সাথে সম্পর্কিত। চিপসেটে আট-বিট পোর্ট রয়েছে। যেকোনো দুটি পরপর 8-বিট পোর্টকে 16-বিট পোর্ট হিসাবে বিবেচনা করা যেতে পারে এবং যে কোনো চারটি পরপর পোর্ট একটি 32-বিট পোর্ট হতে পারে। এই পদ্ধতিতে, প্রসেসর একটি বাহ্যিক ডিভাইসে বা থেকে 8, 16, বা 32 বিট স্থানান্তর করতে পারে।

তথ্য দুটি উপায়ে প্রসেসর এবং একটি অভ্যন্তরীণ পোর্টের মধ্যে স্থানান্তর করা যেতে পারে: মেমরি-ম্যাপ করা ইনপুট/আউটপুট হিসাবে পরিচিত বা একটি পৃথক ইনপুট/আউটপুট ঠিকানা স্থান ব্যবহার করে। মেমরি-ম্যাপ করা I/O হল 6502 প্রসেসরের সাথে যা ঘটে যেখানে পোর্ট ঠিকানাগুলি আসলে পুরো মেমরি স্পেসের অংশ। এই ক্ষেত্রে, একটি নির্দিষ্ট ঠিকানা অবস্থানে ডেটা পাঠানোর সময়, এটি একটি পোর্টে যায়, মেমরি ব্যাঙ্কে নয়। পোর্টগুলির একটি পৃথক I/O ঠিকানা স্থান থাকতে পারে। এই পরবর্তী ক্ষেত্রে, সমস্ত মেমরি ব্যাঙ্ক শূন্য থেকে তাদের ঠিকানা আছে. 0000H থেকে FFFF16 পর্যন্ত একটি পৃথক ঠিকানা পরিসর রয়েছে। এগুলি চিপসেটের পোর্টগুলি ব্যবহার করে। মেমরি-ম্যাপ করা I/O এবং পৃথক I/O ঠিকানা স্থানের মধ্যে বিভ্রান্ত না হওয়ার জন্য মাদারবোর্ডটি প্রোগ্রাম করা হয়েছে।

মেমরি-ম্যাপ করা I/O

এটির সাহায্যে, পোর্টগুলিকে মেমরি অবস্থান হিসাবে বিবেচনা করা হয় এবং মেমরি এবং µP এর মধ্যে ব্যবহার করার জন্য সাধারণ অপকোডগুলি µP এবং পোর্টের মধ্যে ডেটা স্থানান্তরের জন্য ব্যবহৃত হয়। সুতরাং, F000H ঠিকানায় একটি পোর্ট থেকে µP রেজিস্টার RAX:EAX:AX:AL-এ একটি বাইট সরাতে, নিম্নলিখিতগুলি করুন:

MOV AL, [F000H]

একটি স্ট্রিং মেমরি থেকে একটি পোর্টে সরানো যেতে পারে এবং এর বিপরীতে। উদাহরণ:

MOVS [F000H], [C000H] ; উৎস হল C000H, এবং গন্তব্য হল F000H এ পোর্ট।

পৃথক I/O ঠিকানা স্থান

এর সাথে ইনপুট এবং আউটপুটের জন্য বিশেষ নির্দেশাবলী ব্যবহার করতে হবে।

একক আইটেম স্থানান্তর

স্থানান্তরের জন্য প্রসেসর রেজিস্টার হল RAX। প্রকৃতপক্ষে, এটি হল RAX: EAX ডাবলওয়ার্ডের জন্য, RAX: EAX: AX শব্দের জন্য এবং RAX: EAX: AX: AL বাইটের জন্য৷ সুতরাং, FFF0h এ একটি পোর্ট থেকে RAX:EAX:AX:AL-তে একটি বাইট স্থানান্তর করতে, নিম্নলিখিতটি টাইপ করুন:

IN AL, [FFF0H]

বিপরীত স্থানান্তরের জন্য, নিম্নলিখিত টাইপ করুন:

আউট [FFF0H], AL

সুতরাং, একক আইটেমগুলির জন্য, নির্দেশাবলী হল IN এবং OUT৷ পোর্ট ঠিকানা RDX:EDX:DX রেজিস্টারেও দেওয়া যেতে পারে।

স্ট্রিং স্থানান্তর

একটি স্ট্রিং মেমরি থেকে একটি চিপসেট পোর্টে স্থানান্তর করা যেতে পারে এবং এর বিপরীতে। FFF0H ঠিকানায় একটি পোর্ট থেকে মেমরিতে একটি স্ট্রিং স্থানান্তর করতে, C100H থেকে শুরু করুন, টাইপ করুন:

আইএনএস [ইএসআই], [ডিএক্স]

যার একই প্রভাব রয়েছে:

INS [EDI], [DX]

প্রোগ্রামারকে RDX:EDX:Dx রেজিস্টারে FFF0H-এর দুই-বাইট পোর্ট ঠিকানা রাখতে হবে এবং RSI:ESI বা RDI:EDI রেজিস্টারে C100H-এর দুই-বাইটের ঠিকানা রাখতে হবে। বিপরীত স্থানান্তরের জন্য, নিম্নলিখিতগুলি করুন:

আইএনএস [ডিএক্স], [ইএসআই]

যার একই প্রভাব রয়েছে:

আইএনএস [ডিএক্স], [ইডিআই]

6.37 x64-এ স্ট্যাক

6502 প্রসেসরের মতো, x64 প্রসেসরেরও RAM এ একটি স্ট্যাক রয়েছে। x64 এর স্ট্যাক 2 হতে পারে 16 = 65,536 বাইট লম্বা বা এটি 2 হতে পারে 32 = 4,294,967,296 বাইট লম্বা। এটি নিচের দিকেও বৃদ্ধি পায়। যখন একটি রেজিস্টারের বিষয়বস্তু স্ট্যাকের উপর ঠেলে দেওয়া হয়, তখন RSP স্ট্যাক পয়েন্টারে সংখ্যা 8 কমে যায়। মনে রাখবেন x64-এর জন্য একটি মেমরি ঠিকানা 64 বিট প্রশস্ত। µP-এ স্ট্যাক পয়েন্টারের মান RAM-তে স্ট্যাকের পরবর্তী অবস্থানে নির্দেশ করে। যখন একটি রেজিস্টারের বিষয়বস্তু (অথবা একটি অপারেন্ডে একটি মান) স্ট্যাক থেকে একটি রেজিস্টারে পপ করা হয়, তখন RSP স্ট্যাক পয়েন্টারে সংখ্যা 8 দ্বারা বৃদ্ধি করা হয়। অপারেটিং সিস্টেম স্ট্যাকের আকার এবং RAM এ কোথায় শুরু হয় তা নির্ধারণ করে। এবং নিচের দিকে বৃদ্ধি পায়। মনে রাখবেন যে একটি স্ট্যাক হল একটি লাস্ট-ইন-ফার্স্ট-আউট (LIFO) কাঠামো যা এই ক্ষেত্রে নীচের দিকে বৃদ্ধি পায় এবং উপরের দিকে সঙ্কুচিত হয়।

স্ট্যাকে µP RBX রেজিস্টারের বিষয়বস্তু পুশ করতে, নিম্নলিখিতগুলি করুন:

পুশ আরবিএক্স

RBX-এ স্ট্যাকের শেষ এন্ট্রিটি পপ করতে, নিম্নলিখিতগুলি করুন:

POP RBX

6.38 x64 এ পদ্ধতি

x64 এর সাবরুটিনটিকে 'প্রক্রিয়া' বলা হয়। স্ট্যাকটি এখানে 6502 µP এর জন্য ব্যবহৃত হওয়ার চেয়ে বেশি ব্যবহৃত হয়। একটি x64 পদ্ধতির জন্য সিনট্যাক্স হল:

proc_name:

পদ্ধতির শরীর

…

অধিকার

চালিয়ে যাওয়ার আগে, লক্ষ্য করুন যে একটি x64 সাবরুটিনের জন্য opcodes এবং লেবেলগুলি (সাধারণভাবে সমাবেশের ভাষা নির্দেশাবলী) কেস সংবেদনশীল। এটি হল proc_name হল PROC_NAME এর মতই। 6502-এর মতো, অ্যাসেম্বলি ভাষার জন্য টেক্সট এডিটরে একটি নতুন লাইনের শুরুতে পদ্ধতির নাম (লেবেল) শুরু হয়। এটি একটি কোলন দ্বারা অনুসরণ করা হয় এবং 6502 এর মতো স্থান এবং অপকোড দ্বারা নয়। সাবরুটিন বডি অনুসরণ করে, RET দিয়ে শেষ হয় এবং 6502 µP এর মতো RTS নয়। 6502-এর মতো, RET সহ শরীরের প্রতিটি নির্দেশ তার লাইনের শুরুতে শুরু হয় না। মনে রাখবেন এখানে একটি লেবেল 8 অক্ষরের বেশি লম্বা হতে পারে। এই পদ্ধতিটি কল করার জন্য, টাইপ করা পদ্ধতির উপরে বা নীচে থেকে, নিম্নলিখিতগুলি করুন:

কল proc_name

6502 এর সাথে, লেবেলের নামটি কল করার জন্য শুধু টাইপ। যাইহোক, এখানে, সংরক্ষিত শব্দ 'CALL' বা 'কল' টাইপ করা হয়েছে, একটি স্থানের পরে পদ্ধতির নাম (সাবরুটিন) অনুসরণ করা হয়েছে।

পদ্ধতির সাথে ডিল করার সময়, সাধারণত দুটি পদ্ধতি থাকে। একটি পদ্ধতি অন্যটিকে কল করে। যে পদ্ধতিটি কল করে (কলের নির্দেশ আছে) তাকে 'কলার' বলা হয়, এবং যে পদ্ধতিটি কল করা হয় তাকে 'ক্যালি' বলা হয়। অনুসরণ করার জন্য একটি কনভেনশন (নিয়ম) আছে।

কলারের নিয়ম

একটি সাবরুটিন আহ্বান করার সময় কলারকে নিম্নলিখিত নিয়মগুলি মেনে চলতে হবে:

1. একটি সাবরুটিন কল করার আগে, কলারকে নির্দিষ্ট রেজিস্টারের বিষয়বস্তু সংরক্ষণ করা উচিত যা স্ট্যাকের জন্য কলার-সংরক্ষিত হিসাবে মনোনীত করা হয়েছে। কলার-সংরক্ষিত রেজিস্টারগুলি হল R10, R11, এবং যে কোনও রেজিস্টার যাতে প্যারামিটারগুলি রাখা হয় (RDI, RSI, RDX, RCX, R8, R9)। যদি এই রেজিস্টারগুলির বিষয়বস্তুগুলিকে সাবরুটিন কল জুড়ে সংরক্ষণ করতে হয়, তবে সেগুলিকে RAM-তে সংরক্ষণ করার পরিবর্তে স্ট্যাকের উপর পুশ করুন৷ এগুলি করতে হবে কারণ রেজিস্টারগুলি আগের বিষয়বস্তু মুছে ফেলার জন্য কলির দ্বারা ব্যবহার করতে হবে।

2. যদি পদ্ধতিটি উদাহরণ স্বরূপ দুটি সংখ্যা যোগ করা হয়, তাহলে দুটি সংখ্যা হল প্যারামিটার যা স্ট্যাকে পাস করা হবে। সাবরুটিনে প্যারামিটারগুলি পাস করতে, তাদের মধ্যে ছয়টি ক্রমানুসারে নিম্নলিখিত নিবন্ধগুলিতে রাখুন: RDI, RSI, RDX, RCX, R8, R9। সাবরুটিনে ছয়টির বেশি প্যারামিটার থাকলে, বাকিগুলোকে স্ট্যাকের ওপরে বিপরীত ক্রমে ঠেলে দিন (যেমন, শেষ পরামিতি প্রথমে)। যেহেতু স্ট্যাকটি নিচের দিকে বাড়তে থাকে, অতিরিক্ত প্যারামিটারের প্রথমটি (সত্যিই সপ্তম প্যারামিটার) সর্বনিম্ন ঠিকানায় সংরক্ষিত হয় (প্যারামিটারের এই পরিবর্তনটি ঐতিহাসিকভাবে ফাংশন (সাবরুটিনগুলি) পরিবর্তনশীল সংখ্যক প্যারামিটারের সাথে পাস করার অনুমতি দেওয়ার জন্য ব্যবহৃত হয়েছিল)।

3. সাবরুটিন (প্রক্রিয়া) কল করতে, কল নির্দেশ ব্যবহার করুন। এই নির্দেশটি স্ট্যাকের প্যারামিটারের উপরে (সর্বনিম্ন অবস্থান) এবং শাখাগুলিকে সাবরুটিন কোডে রিটার্ন ঠিকানা রাখে।

4. সাবরুটিন ফিরে আসার পরে (অর্থাৎ অবিলম্বে কলের নির্দেশনা অনুসরণ করে), কলকারীকে অবশ্যই স্ট্যাক থেকে যেকোনো অতিরিক্ত প্যারামিটার (ছয়টির বাইরে যা রেজিস্টারে সংরক্ষিত আছে) সরিয়ে ফেলতে হবে। কলটি সম্পাদিত হওয়ার আগে এটি স্ট্যাকটিকে তার অবস্থায় পুনরুদ্ধার করে।

5. কলকারী RAX রেজিস্টারে সাবরুটিনের রিটার্ন মান (ঠিকানা) খুঁজে পাওয়ার আশা করতে পারেন।

6. কলকারী কলার-সংরক্ষিত রেজিস্টারের বিষয়বস্তু (R10, R11, এবং প্যারামিটার পাসিং রেজিস্টারে যেকোনও) স্ট্যাকের থেকে পপ অফ করে পুনরুদ্ধার করে। কলকারী অনুমান করতে পারেন যে সাবরুটিন দ্বারা অন্য কোন রেজিস্টার পরিবর্তন করা হয়নি।

কলিং কনভেনশনটি যেভাবে গঠন করা হয়েছে তার কারণে, এটি সাধারণত এমন হয় যে এই ধাপগুলির কিছু (বা বেশিরভাগ) স্ট্যাকের কোনো পরিবর্তন করবে না। উদাহরণস্বরূপ, যদি ছয় বা তার কম পরামিতি থাকে, তবে সেই ধাপে স্ট্যাকের উপরে কিছুই ধাক্কা দেওয়া হয় না। অনুরূপভাবে, প্রোগ্রামাররা (এবং কম্পাইলাররা) সাধারণত অতিরিক্ত ধাক্কা এবং পপ প্রতিরোধ করার জন্য 1 এবং 6 ধাপে কলার-সংরক্ষিত রেজিস্টারের বাইরে যে ফলাফলগুলি তাদের যত্ন করে তা রাখে।

একটি সাবরুটিনে প্যারামিটারগুলি পাস করার আরও দুটি উপায় রয়েছে, তবে এই অনলাইন ক্যারিয়ার কোর্সে সেগুলিকে সম্বোধন করা হবে না। তাদের মধ্যে একজন সাধারণ-উদ্দেশ্য রেজিস্টারের পরিবর্তে স্ট্যাক নিজেই ব্যবহার করে।

ক্যালির নিয়ম

নামক সাবরুটিনের সংজ্ঞা নিম্নলিখিত নিয়মগুলি মেনে চলা উচিত:

1. রেজিস্টার ব্যবহার করে বা স্ট্যাকের উপর স্থান তৈরি করে স্থানীয় ভেরিয়েবলগুলি (প্রক্রিয়ার মধ্যে তৈরি করা ভেরিয়েবল) বরাদ্দ করুন। স্তুপ নিচের দিকে বৃদ্ধি স্মরণ. সুতরাং, স্ট্যাকের শীর্ষে স্থান তৈরি করতে, স্ট্যাক পয়েন্টারটি হ্রাস করা উচিত। স্ট্যাক পয়েন্টার যে পরিমাণে হ্রাস পায় তা নির্ভর করে স্থানীয় ভেরিয়েবলের প্রয়োজনীয় সংখ্যার উপর। উদাহরণস্বরূপ, যদি একটি স্থানীয় ফ্লোট এবং একটি স্থানীয় দীর্ঘ (মোট 12 বাইট) প্রয়োজন হয়, তাহলে এই স্থানীয় ভেরিয়েবলগুলির জন্য স্থান তৈরি করতে স্ট্যাক পয়েন্টারকে 12 দ্বারা হ্রাস করতে হবে। C এর মত একটি উচ্চ-স্তরের ভাষায়, এর মানে হল মানগুলি বরাদ্দ না করে (শুরু করা) ভেরিয়েবল ঘোষণা করা।

2. এর পরে, যে কোনও রেজিস্টারের মানগুলি যেগুলি মনোনীত কলী-সংরক্ষিত (সাধারণ উদ্দেশ্যের রেজিস্টারগুলি কলার দ্বারা সংরক্ষিত নয়) যেগুলি ফাংশন দ্বারা ব্যবহৃত হয় সেগুলি অবশ্যই সংরক্ষণ করতে হবে৷ রেজিস্টার সংরক্ষণ করতে, স্ট্যাকের উপর তাদের ধাক্কা. কলে-সংরক্ষিত রেজিস্টারগুলি হল RBX, RBP, এবং R12 থেকে R15 (RSP এছাড়াও কল কনভেনশন দ্বারা সংরক্ষিত, কিন্তু এই ধাপে স্ট্যাকের উপর পুশ করার প্রয়োজন নেই)।

এই তিনটি ক্রিয়া সম্পাদন করার পরে, সাবরুটিনের প্রকৃত ক্রিয়াকলাপ এগিয়ে যেতে পারে। সাবরুটিন ফিরে আসার জন্য প্রস্তুত হলে, কল কনভেনশন নিয়ম চলতে থাকে।

3. সাবরুটিন হয়ে গেলে, সাবরুটিনের রিটার্ন মানটি RAX-এ স্থাপন করা উচিত যদি এটি ইতিমধ্যে সেখানে না থাকে।

4. সাবরুটিনকে অবশ্যই সংশোধিত যেকোন কলী-সংরক্ষিত রেজিস্টারের (RBX, RBP, এবং R12 থেকে R15) পুরানো মান পুনরুদ্ধার করতে হবে। রেজিস্টার বিষয়বস্তু স্ট্যাক থেকে পপিং দ্বারা পুনরুদ্ধার করা হয়. মনে রাখবেন যে রেজিস্টারগুলিকে যে বিপরীত ক্রমে ধাক্কা দেওয়া হয়েছিল সেই ক্রমে পপ করা উচিত।

5. এর পরে, আমরা স্থানীয় ভেরিয়েবল ডিলকেট করি। এটি করার সবচেয়ে সহজ উপায় হল RSP-তে একই পরিমাণ যোগ করা যা এটি থেকে ধাপ 1 এ বিয়োগ করা হয়েছিল।

6. অবশেষে, আমরা একটি রিট নির্দেশনা কার্যকর করে কলারের কাছে ফিরে আসি। এই নির্দেশটি স্ট্যাক থেকে উপযুক্ত রিটার্ন ঠিকানা খুঁজে বের করবে এবং সরিয়ে দেবে।

অন্য একটি সাবরুটিন কল করার জন্য একজন কলার সাবরুটিনের বডির একটি উদাহরণ যা হল “myFunc” নিম্নরূপ (মন্তব্য পড়ুন):

; একটি ফাংশন 'myFunc' কল করতে চান যা তিনটি লাগে

; পূর্ণসংখ্যা প্যারামিটার। প্রথম প্যারামিটারটি RAX-এ রয়েছে।

; দ্বিতীয় প্যারামিটার হল ধ্রুবক 456. তৃতীয়

; প্যারামিটার মেমরি অবস্থান 'ভেরিয়েবল' এ আছে

push rdi ; rdi একটি param হবে, তাই এটি সংরক্ষণ করুন

; long retVal = myFunc ( x , 456 , z );

mov rdi, rax; RDI তে প্রথম প্যারামিটার রাখুন

mov rsi, 456 ; RSI তে দ্বিতীয় প্যারামিটার রাখুন

mov rdx , [ভেরিয়েবল] ; RDX এ তৃতীয় প্যারামিটার রাখুন

myFunc কল করুন; ফাংশন কল

পপ আরডিআই; সংরক্ষিত RDI মান পুনরুদ্ধার করুন

; myFunc এর রিটার্ন মান এখন RAX-এ উপলব্ধ

একটি callee ফাংশন (myFunc) এর একটি উদাহরণ হল (মন্তব্য পড়ুন):

myFunc:

; ∗∗∗ স্ট্যান্ডার্ড সাবরুটিন প্রস্তাবনা ∗∗∗

সাব আরএসপি, 8; 'সাব' অপকোড ব্যবহার করে একটি 64−বিট স্থানীয় পরিবর্তনশীল (ফলাফল) এর জন্য রুম

পুশ আরবিএক্স; কলী সংরক্ষণ করুন - রেজিস্টার সংরক্ষণ করুন

পুশ আরবিপি; উভয়ই myFunc দ্বারা ব্যবহার করা হবে

; ∗∗∗ সাব রুটিন বডি ∗∗∗

mov rax, rdi; প্যারামিটার 1 থেকে RAX

mov rbp, rsi; প্যারামিটার 2 থেকে RBP

mov rbx, rdx; প্যারামিটার 3 থেকে rb x

mov [ rsp + 1 6 ] , rbx ; স্থানীয় ভেরিয়েবলে rbx রাখুন

যোগ করুন [ rsp + 1 6 ] , rbp ; স্থানীয় ভেরিয়েবলে rbp যোগ করুন

mov rax , [ আরএসপি +16 ] ; RAX-এ স্থানীয় ভেরিয়েবলের mov বিষয়বস্তু

; (রিটার্ন মান/চূড়ান্ত ফলাফল)

; ∗∗∗ স্ট্যান্ডার্ড সাবরুটিন এপিলগ ∗∗∗

পপ আরবিপি; কলী সংরক্ষণ রেজিস্টার পুনরুদ্ধার করুন

পপ আরবিএক্স; যখন ধাক্কা দেওয়া হয় তার বিপরীত

rsp যোগ করুন, 8; স্থানীয় পরিবর্তনশীল (গুলি) ডিলোকেট করুন। 8 মানে 8 বাইট

ret; স্ট্যাক থেকে পপ শীর্ষ মান, সেখানে ঝাঁপ দাও

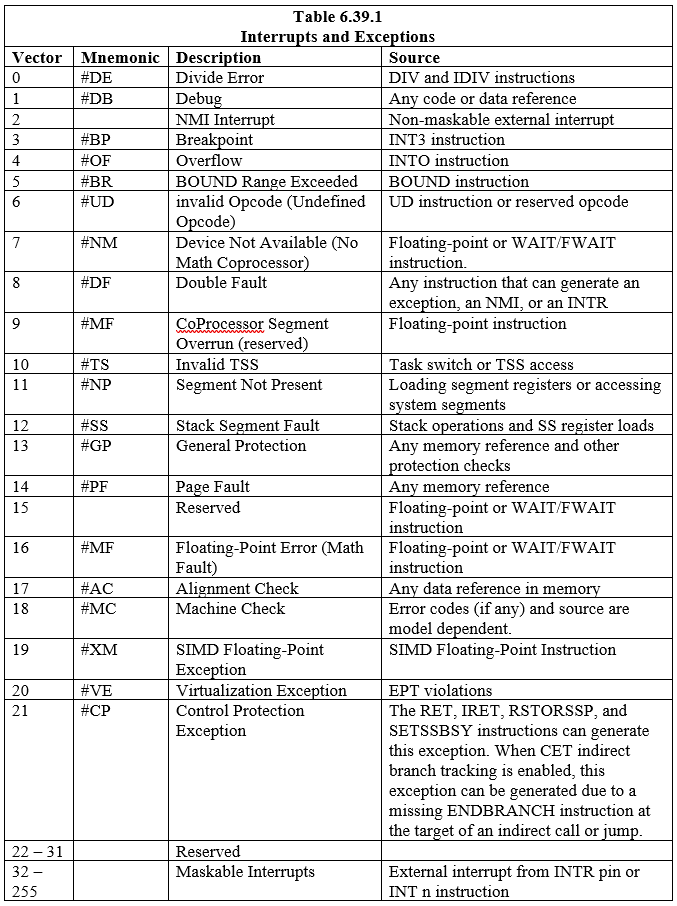

6.39 x64 এর জন্য বাধা এবং ব্যতিক্রম

প্রসেসর প্রোগ্রাম এক্সিকিউশন, ইন্টারাপ্ট এবং ব্যতিক্রম বাধাগ্রস্ত করার জন্য দুটি প্রক্রিয়া প্রদান করে:

- একটি বিঘ্ন হল একটি অ্যাসিঙ্ক্রোনাস (যেকোন সময় ঘটতে পারে) ইভেন্ট যা সাধারণত একটি I/O ডিভাইস দ্বারা ট্রিগার হয়।

- একটি ব্যতিক্রম হল একটি সিঙ্ক্রোনাস ইভেন্ট (কোডটি কার্যকর হওয়ার সাথে সাথে ঘটে, প্রি-প্রোগ্রাম করা, কিছু ঘটনার উপর ভিত্তি করে) যা একটি নির্দেশ কার্যকর করার সময় প্রসেসর এক বা একাধিক পূর্বনির্ধারিত শর্ত সনাক্ত করে তখন তৈরি হয়। ব্যতিক্রমের তিনটি শ্রেণি নির্দিষ্ট করা হয়েছে: ফল্ট, ফাঁদ এবং গর্ভপাত।

প্রসেসর মূলত একইভাবে বাধা এবং ব্যতিক্রমগুলির প্রতিক্রিয়া জানায়। যখন একটি বাধা বা ব্যতিক্রম সংকেত করা হয়, প্রসেসর বর্তমান প্রোগ্রাম বা টাস্কের কার্য সম্পাদন বন্ধ করে দেয় এবং একটি হ্যান্ডলার পদ্ধতিতে স্যুইচ করে যা বিঘ্ন বা ব্যতিক্রম অবস্থা পরিচালনা করার জন্য বিশেষভাবে লেখা হয়। প্রসেসর ইন্টারাপ্ট ডিসক্রিপ্টর টেবিল (IDT) এ একটি এন্ট্রির মাধ্যমে হ্যান্ডলার পদ্ধতিতে অ্যাক্সেস করে। হ্যান্ডলার যখন বাধা বা ব্যতিক্রম পরিচালনা সম্পূর্ণ করে, তখন প্রোগ্রাম নিয়ন্ত্রণ বাধাপ্রাপ্ত প্রোগ্রাম বা টাস্কে ফিরে আসে।

অপারেটিং সিস্টেম, এক্সিকিউটিভ, এবং/অথবা ডিভাইস ড্রাইভার সাধারণত অ্যাপ্লিকেশন প্রোগ্রাম বা কাজ থেকে স্বাধীনভাবে বাধা এবং ব্যতিক্রমগুলি পরিচালনা করে। অ্যাপ্লিকেশন প্রোগ্রামগুলি, যাইহোক, একটি অপারেটিং সিস্টেমে অন্তর্ভূক্ত বা অ্যাসেম্বলি-ভাষা কলের মাধ্যমে এক্সিকিউটিভ হ্যান্ডলারে প্রবেশ করতে পারে।

আঠারো (18) পূর্বনির্ধারিত বাধা এবং ব্যতিক্রম, যা IDT-তে এন্ট্রির সাথে যুক্ত, সংজ্ঞায়িত করা হয়েছে। দুইশত চব্বিশ (224) ব্যবহারকারী সংজ্ঞায়িত বাধাগুলিও তৈরি করা যেতে পারে এবং টেবিলের সাথে যুক্ত করা যেতে পারে। IDT-তে প্রতিটি বাধা এবং ব্যতিক্রম একটি সংখ্যা দ্বারা চিহ্নিত করা হয় যাকে 'ভেক্টর' বলা হয়। সারণি 6.39.1 আইডিটি এবং তাদের নিজ নিজ ভেক্টরের এন্ট্রি সহ বাধা এবং ব্যতিক্রমগুলির তালিকা করে। ভেক্টর 0 থেকে 8, 10 থেকে 14, এবং 16 থেকে 19 হল পূর্বনির্ধারিত বাধা এবং ব্যতিক্রম। 32 থেকে 255 ভেক্টরগুলি সফ্টওয়্যার-সংজ্ঞায়িত বাধাগুলির (ব্যবহারকারী) জন্য যা হয় সফ্টওয়্যার বাধা বা মাস্কযোগ্য হার্ডওয়্যার বাধাগুলির জন্য।

যখন প্রসেসর একটি বাধা বা ব্যতিক্রম সনাক্ত করে, তখন এটি নিম্নলিখিত জিনিসগুলির মধ্যে একটি করে:

- হ্যান্ডলার পদ্ধতিতে একটি অন্তর্নিহিত কল চালান

- একটি হ্যান্ডলার টাস্কে একটি অন্তর্নিহিত কল চালান

6.4 64-বিট এআরএম কম্পিউটার আর্কিটেকচার বেসিকস

এআরএম আর্কিটেকচারগুলি RISC প্রসেসরের একটি পরিবারকে সংজ্ঞায়িত করে যা বিভিন্ন ধরণের অ্যাপ্লিকেশনে ব্যবহারের জন্য উপযুক্ত। ARM হল একটি লোড/স্টোর আর্কিটেকচার যেটির সাথে ALU (Arithmetic Logic Unit) অপারেশনের মতো কোনো প্রক্রিয়াকরণের আগে মেমরি থেকে একটি রেজিস্টারে ডেটা লোড করা প্রয়োজন। একটি পরবর্তী নির্দেশনা ফলাফলটিকে মেমরিতে ফিরিয়ে রাখে। যদিও এটি x86 এবং x64 আর্কিটেকচার থেকে একধাপ পিছিয়ে বলে মনে হতে পারে, যা সরাসরি মেমরির অপারেন্ডগুলিতে একটি একক নির্দেশে কাজ করে (অবশ্যই প্রসেসর রেজিস্টার ব্যবহার করে), লোড/স্টোর পদ্ধতি, বাস্তবে, বেশ কয়েকটি অনুক্রমিক অপারেশনের অনুমতি দেয়। অনেকগুলি প্রসেসর রেজিস্টারের মধ্যে একটিতে লোড হয়ে গেলে একটি অপারেন্ডে উচ্চ গতিতে সঞ্চালিত হবে। এআরএম প্রসেসরগুলিতে সামান্য এন্ডিয়াননেস বা বড়-এন্ডিয়াননেসের বিকল্প রয়েছে। ডিফল্ট ARM 64 সেটিং হল সামান্য-এন্ডিয়ান যা কনফিগারেশন যা সাধারণত অপারেটিং সিস্টেম দ্বারা ব্যবহৃত হয়। 64-বিট এআরএম আর্কিটেকচার আধুনিক এবং এটি 32-বিট এআরএম আর্কিটেকচার প্রতিস্থাপন করতে সেট করা হয়েছে।

বিঃদ্রঃ : 64-বিট ARM µP-এর জন্য প্রতিটি নির্দেশ 4 বাইট (32 বিট) দীর্ঘ৷

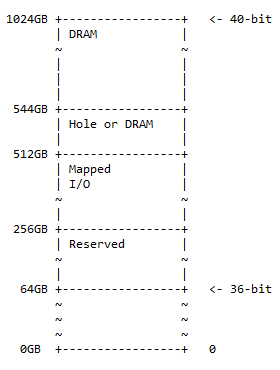

6.41 64-বিট এআরএম রেজিস্টার সেট

64-বিট ARM µP-এর জন্য 64-বিট রেজিস্টারের 31টি সাধারণ উদ্দেশ্য রয়েছে। নিম্নলিখিত চিত্রটি সাধারণ-উদ্দেশ্য রেজিস্টার এবং কিছু গুরুত্বপূর্ণ রেজিস্টার দেখায়:

চিত্র.4.11.1 64-বিট সাধারণ উদ্দেশ্য এবং কিছু গুরুত্বপূর্ণ রেজিস্টার

সাধারণ-উদ্দেশ্য রেজিস্টারগুলিকে X0 থেকে X30 হিসাবে উল্লেখ করা হয়। প্রতিটি রেজিস্টারের জন্য প্রথম 32-বিট অংশকে W0 থেকে W30 হিসাবে উল্লেখ করা হয়। যখন 32 বিট এবং 64 বিটের মধ্যে পার্থক্যের উপর জোর দেওয়া হয় না, তখন 'R' উপসর্গ ব্যবহার করা হয়। উদাহরণস্বরূপ, R14 W14 বা X14 বোঝায়।

6502 µP এর একটি 16-বিট প্রোগ্রাম কাউন্টার রয়েছে এবং এটি 2-কে সম্বোধন করতে পারে 16 মেমরি বাইট অবস্থান। 64-বিট ARM µP এর একটি 64-বিট প্রোগ্রাম কাউন্টার রয়েছে এবং এটি 2 পর্যন্ত অ্যাড্রেস করতে পারে 64 = 1.844674407 x 1019 (আসলে 18,446,744,073,709,551,616) মেমরি বাইট অবস্থান। প্রোগ্রাম কাউন্টারে কার্যকর করা পরবর্তী নির্দেশের ঠিকানা থাকে। ARM64 বা AArch64-এর নির্দেশের দৈর্ঘ্য সাধারণত চার বাইট। মেমরি থেকে প্রতিটি নির্দেশ আনার পরে প্রসেসর স্বয়ংক্রিয়ভাবে এই রেজিস্টারটি চার দ্বারা বৃদ্ধি করে।

স্ট্যাক পয়েন্টার রেজিস্টার বা SP 31টি সাধারণ উদ্দেশ্য রেজিস্টারের মধ্যে নেই। যেকোনো আর্কিটেকচারের স্ট্যাক পয়েন্টার মেমরির শেষ স্ট্যাক এন্ট্রির দিকে নির্দেশ করে। ARM-64 এর জন্য, স্ট্যাকটি নীচের দিকে বৃদ্ধি পায়।

6502 µP এর একটি 8-বিট প্রসেসর স্ট্যাটাস রেজিস্টার রয়েছে। ARM64 এর সমতুল্যকে PSTATE রেজিস্টার বলা হয়। এই রেজিস্টার ফ্ল্যাগগুলি সঞ্চয় করে যা অপারেশনের ফলাফলের জন্য এবং প্রসেসর (µP) নিয়ন্ত্রণের জন্য ব্যবহৃত হয়। এটি 32-বিট প্রশস্ত। নিম্নলিখিত টেবিলটি PSTATE রেজিস্টারে সাধারণত ব্যবহৃত বিটগুলির নাম, সূচক এবং অর্থ দেয়:

| সারণি 6.41.1 সর্বাধিক ব্যবহৃত PSTATE পতাকা (বিট) |

||

|---|---|---|

| প্রতীক | বিট | উদ্দেশ্য |

| এম | 0-3 | মোড: বর্তমান এক্সিকিউশন প্রিভিলেজ লেভেল (USR, SVC, এবং আরও)। |

| টি | 4 | থাম্ব: এটি সেট করা হয় যদি T32 (থাম্ব) নির্দেশ সেট সক্রিয় থাকে। যদি পরিষ্কার হয়, ARM নির্দেশ সেট সক্রিয়। ব্যবহারকারী কোড সেট এবং এই বিট পরিষ্কার করতে পারেন. |

| এবং | 9 | Endianness: এই বিট সেট করা বিগ-এন্ডিয়ান মোড সক্ষম করে। পরিষ্কার হলে, লিটল-এন্ডিয়ান মোড সক্রিয়। ডিফল্ট হল লিটল-এন্ডিয়ান মোড। |

| প্র | 27 | ক্রমবর্ধমান স্যাচুরেশন পতাকা: এটি সেট করা হয় যদি, অপারেশনের একটি সিরিজের কোনো সময়ে, একটি ওভারফ্লো বা স্যাচুরেশন ঘটে |

| ভিতরে | 28 | ওভারফ্লো পতাকা: এটি সেট করা হয় যদি অপারেশনের ফলে একটি স্বাক্ষরিত ওভারফ্লো হয়। |

| গ | 29 | ক্যারি পতাকা: এটি নির্দেশ করে যে যোগটি একটি বহন তৈরি করেছে বা বিয়োগ একটি ধার তৈরি করেছে। |

| সঙ্গে | 30 | শূন্য পতাকা: এটি সেট করা হয় যদি একটি অপারেশনের ফলাফল শূন্য হয়। |

| এন | 31 | নেতিবাচক পতাকা: এটি সেট করা হয় যদি একটি অপারেশনের ফলাফল নেতিবাচক হয়। |

ARM-64 µP এর আরও অনেক রেজিস্টার রয়েছে।

SIMD

SIMD মানে একক নির্দেশনা, একাধিক ডেটা। এর মানে হল যে একটি অ্যাসেম্বলি ভাষার নির্দেশনা একটি মাইক্রোপ্রসেসরে একই সময়ে একাধিক ডেটাতে কাজ করতে পারে। SIMD এবং ফ্লোটিং-পয়েন্ট অপারেশনের সাথে ব্যবহারের জন্য বত্রিশটি 128 বিট প্রশস্ত রেজিস্টার রয়েছে।

6.42 মেমরি ম্যাপিং

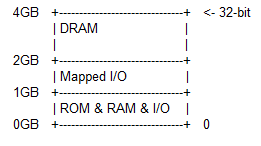

RAM এবং DRAM উভয়ই র্যান্ডম অ্যাক্সেস মেমোরি। DRAM RAM এর চেয়ে ধীর গতিতে কাজ করে। DRAM RAM এর চেয়ে সস্তা। মেমরিতে 32 গিগাবাইট (GB) এর বেশি অবিরত DRAM থাকলে, আরও মেমরি পরিচালনার সমস্যা হবে: 32 GB = 32 x 1024 x 1024 x 1024 বাইট। একটি সম্পূর্ণ মেমরি স্পেস যা 32 GB থেকে অনেক বড়, 32 GB-এর উপরে DRAM-কে আরও ভাল মেমরি ম্যানেজমেন্টের জন্য র্যামের সাথে ছেদ করা উচিত। ARM-64 মেমরি ম্যাপ বোঝার জন্য, আপনাকে প্রথমে 32-বিট ARM সেন্ট্রাল প্রসেসিং ইউনিট (CPU) এর জন্য 4GB মেমরি ম্যাপ বুঝতে হবে। CPU মানে µP। একটি 32-বিট কম্পিউটারের জন্য, সর্বাধিক মেমরি ঠিকানাযোগ্য স্থান হল 2 32 = 4 x 2 10 x 2 10 x 2 10 = 4 x 1024 x 1024 x 1024 = 4,294,967,296 = 4GB।

32-বিট এআরএম মেমরি ম্যাপ

একটি 32-বিট এআরএম-এর মেমরি ম্যাপ হল:

একটি 32-বিট কম্পিউটারের জন্য, পুরো মেমরির সর্বাধিক আকার 4GB। 0GB ঠিকানা থেকে 1GB ঠিকানা হল ROM অপারেটিং সিস্টেম, RAM এবং I/O অবস্থান। ROM OS, RAM, এবং I/O ঠিকানাগুলির সম্পূর্ণ ধারণা সম্ভাব্য 6502 CPU সহ কমোডোর-64-এর পরিস্থিতির মতো। কমোডোর-64-এর জন্য OS ROM মেমরি স্পেসের উপরের প্রান্তে রয়েছে। এখানে রম ওএস কমোডোর-64 এর চেয়ে অনেক বড় এবং এটি পুরো মেমরি অ্যাড্রেস স্পেসের শুরুতে রয়েছে। অন্যান্য আধুনিক কম্পিউটারের সাথে তুলনা করলে, এখানে ROM OS সম্পূর্ণ, এই অর্থে যে এটি তাদের হার্ড ড্রাইভে OS এর পরিমাণের সাথে তুলনীয়। ROM ইন্টিগ্রেটেড সার্কিটগুলিতে OS থাকার দুটি প্রধান কারণ রয়েছে: 1) ARM CPU গুলি বেশিরভাগ স্মার্টফোনের মতো ছোট ডিভাইসগুলিতে ব্যবহৃত হয়। অনেক হার্ড ড্রাইভ স্মার্টফোন এবং অন্যান্য ছোট ডিভাইসের চেয়ে বড়, 2) নিরাপত্তার জন্য। যখন OS শুধুমাত্র পঠনযোগ্য মেমরিতে থাকে, তখন এটি হ্যাকারদের দ্বারা দূষিত (অংশগুলি ওভাররাইট) হতে পারে না। কমডোর-64-এর তুলনায় RAM বিভাগ এবং ইনপুট/আউটপুট বিভাগগুলিও অনেক বড়।

যখন 32-বিট রম ওএসের সাথে পাওয়ার চালু করা হয়, হাইভিইসি সক্রিয় থাকলে ওএসকে অবশ্যই 0x00000000 ঠিকানা বা 0xFFFF0000 ঠিকানা থেকে (বুট থেকে) শুরু করতে হবে। সুতরাং, রিসেট পর্বের পরে যখন পাওয়ার চালু করা হয়, তখন CPU হার্ডওয়্যার প্রোগ্রাম কাউন্টারে 0x00000000 বা 0xFFFF0000 লোড করে। '0x' উপসর্গ মানে হেক্সাডেসিমাল। ARMv8 64bit CPU-এর বুট ঠিকানা একটি সংজ্ঞায়িত বাস্তবায়ন। যাইহোক, লেখক পিছিয়ে থাকা সামঞ্জস্যের জন্য কম্পিউটার ইঞ্জিনিয়ারকে 0x00000000 বা 0xFFFF0000 থেকে শুরু করার পরামর্শ দেন।

1GB থেকে 2GB পর্যন্ত ম্যাপ করা ইনপুট/আউটপুট। ম্যাপ করা I/O এবং শুধুমাত্র I/O এর মধ্যে পার্থক্য রয়েছে যা 0GB এবং 1GB এর মধ্যে পাওয়া যায়। I/O এর সাথে, প্রতিটি পোর্টের ঠিকানা কমোডোর-64-এর মতোই স্থির করা হয়েছে। ম্যাপ করা I/O এর সাথে, প্রতিটি পোর্টের ঠিকানা কম্পিউটারের প্রতিটি অপারেশনের জন্য অগত্যা একই নয় (গতিশীল)।

2GB থেকে 4GB পর্যন্ত DRAM। এটি প্রত্যাশিত (বা স্বাভাবিক) RAM। DRAM এর অর্থ হল Dynamic RAM, কম্পিউটার অপারেশন চলাকালীন একটি পরিবর্তনের ঠিকানার অনুভূতি নয় কিন্তু এই অর্থে যে শারীরিক র্যামের প্রতিটি কোষের মান প্রতিটি ঘড়ির স্পন্দনে রিফ্রেশ করতে হবে।

বিঃদ্রঃ :

- 0x0000,0000 থেকে 0x0000, FFFF হল OS ROM।

- 0x0001,0000 থেকে 0x3FFF, FFFF, আরও রম, তারপর RAM এবং তারপর কিছু I/O হতে পারে।

- 0x4000,0000 থেকে 0x7FFF, FFFF, একটি অতিরিক্ত I/O এবং/অথবা ম্যাপ করা I/O অনুমোদিত।

- 0x8000,0000 থেকে 0xFFFF, FFFF হল প্রত্যাশিত DRAM।

এর মানে হল যে প্রত্যাশিত DRAM 2GB মেমরি সীমানা থেকে শুরু করতে হবে না, অনুশীলনে। মাদারবোর্ডে স্লট করা পর্যাপ্ত শারীরিক র্যাম ব্যাঙ্ক না থাকলে কেন প্রোগ্রামারকে আদর্শ সীমানাকে সম্মান করা উচিত? এর কারণ হল সমস্ত RAM ব্যাঙ্কের জন্য গ্রাহকের কাছে পর্যাপ্ত টাকা নেই।

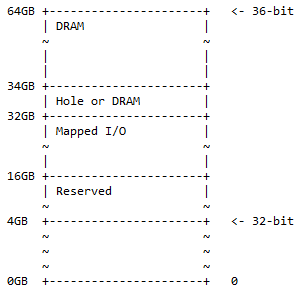

36-বিট এআরএম মেমরি ম্যাপ

একটি 64-বিট এআরএম কম্পিউটারের জন্য, সমস্ত 32 বিট পুরো মেমরিকে অ্যাড্রেস করতে ব্যবহৃত হয়। একটি 64-বিট এআরএম কম্পিউটারের জন্য, প্রথম 36 বিটগুলি পুরো মেমরিকে অ্যাড্রেস করতে ব্যবহার করা যেতে পারে যা এই ক্ষেত্রে 2 36 = 68,719,476,736 = 64GB। এটি ইতিমধ্যে অনেক স্মৃতি। সাধারণ কম্পিউটারের আজ এই পরিমাণ মেমরির প্রয়োজন নেই। এটি এখনও মেমরির সর্বোচ্চ পরিসর পর্যন্ত নয় যা 64 বিট দ্বারা অ্যাক্সেস করা যেতে পারে। ARM CPU-এর জন্য 36-বিটের মেমরি ম্যাপ হল:

0GB ঠিকানা থেকে 4GB ঠিকানা পর্যন্ত 32-বিট মেমরি ম্যাপ। 'সংরক্ষিত' মানে ব্যবহৃত হয় না এবং ভবিষ্যতে ব্যবহারের জন্য রাখা হয়। এটি সেই স্থানের জন্য মাদারবোর্ডে স্লট করা শারীরিক মেমরি ব্যাঙ্ক হতে হবে না। এখানে, DRAM এবং ম্যাপ করা I/O-এর 32-বিট মেমরি মানচিত্রের মতো একই অর্থ রয়েছে।

নিম্নলিখিত পরিস্থিতি অনুশীলনে পাওয়া যেতে পারে:

- 0x1 0000 0000 – 0x3 FFFF FFFF; সংরক্ষিত ঠিকানার 12GB স্থান ভবিষ্যতে ব্যবহারের জন্য সংরক্ষিত।

- 0x4 0000 0000 – 0x7 FFFF FFFF; ম্যাপ করা I/O গতিশীলভাবে ম্যাপ করা I/O-এর জন্য 16GB ঠিকানার স্থান উপলব্ধ।

- 0x8 0000 0000 – 0x8 7FFF FFFF FFFF; গর্ত বা DRAM। ঠিকানার 2 গিগাবাইট স্থান নিম্নলিখিত যে কোনো একটি থাকতে পারে:

- DRAM ডিভাইস পার্টিশন সক্রিয় করার জন্য হোল (নিম্নলিখিত আলোচনায় বর্ণিত)।

- DRAM।

- 0x8 8000 0000 – 0xF FFFF FFFF; DRAM। DRAM-এর জন্য 30GB ঠিকানার স্থান।

এই মেমরি ম্যাপটি 32-বিট ঠিকানা মানচিত্রের একটি সুপারসেট, অতিরিক্ত স্থান 50% DRAM (1/2) হিসাবে বিভক্ত করা হয়েছে এবং এতে একটি ঐচ্ছিক গর্ত রয়েছে এবং 25% ম্যাপ করা I/O স্থান এবং সংরক্ষিত স্থান (1/4) ) অবশিষ্ট 25% (1/4) 32-বিট মেমরি ম্যাপের জন্য ½ + ¼ + ¼ = 1।

বিঃদ্রঃ : 32 বিট থেকে 360 বিট হল 36 বিটের সবচেয়ে উল্লেখযোগ্য দিকে 4 বিটের সংযোজন।

40-বিট মেমরি ম্যাপ

40-বিট ঠিকানা মানচিত্রটি 36-বিট ঠিকানা মানচিত্রের একটি সুপারসেট এবং এটিতে একটি ঐচ্ছিক গর্তের 50% DRAM এর একই প্যাটার্ন অনুসরণ করে, 25% ম্যাপ করা I/O স্থান এবং সংরক্ষিত স্থান এবং বাকি 25% পূর্ববর্তী মেমরি মানচিত্রের জন্য স্থান (36-বিট)। মেমরি মানচিত্রের চিত্রটি হল:

গর্তের আকার হল 544 – 512 = 32GB। নিম্নলিখিত পরিস্থিতি অনুশীলনে পাওয়া যেতে পারে:

- 0x10 0000 0000 – 0x3F FFFF FFFF; সংরক্ষিত ঠিকানার 192GB স্থান ভবিষ্যতে ব্যবহারের জন্য সংরক্ষিত।

- 0x40 0000 0000 – 0x7F FFFF FFFF; ম্যাপ করা I/O 256GB ঠিকানা স্থান গতিশীলভাবে ম্যাপ করা I/O এর জন্য উপলব্ধ।

- 0x80 0000 0000 – 0x87 FFFF FFFF; গর্ত বা DRAM। 32GB অ্যাড্রেস স্পেসে নিম্নলিখিত যেকোন একটি থাকতে পারে:

- DRAM ডিভাইস পার্টিশন সক্রিয় করার জন্য হোল (নিম্নলিখিত আলোচনায় বর্ণিত)

- DRAM

- 0x88 0000 0000 – 0xFF FFFF FFFF; DRAM। DRAM এর জন্য 480GB ঠিকানার স্থান।

বিঃদ্রঃ : 36 বিট থেকে 40 বিট হল 36 বিটের সবচেয়ে উল্লেখযোগ্য দিকে 4 বিটের সংযোজন।

DRAM হোল

32-বিটের বাইরের মেমরি মানচিত্রে, এটি হয় একটি DRAM হোল বা উপরে থেকে DRAM-এর ধারাবাহিকতা। যখন এটি একটি গর্ত হয়, এটি নিম্নরূপ প্রশংসা করা হয়: DRAM হোল একটি বড় DRAM ডিভাইসকে একাধিক ঠিকানা রেঞ্জে ভাগ করার একটি উপায় প্রদান করে। ঐচ্ছিক DRAM গর্ত উচ্চ DRAM ঠিকানা সীমানা শুরুতে প্রস্তাবিত হয়. এটি একটি সরলীকৃত ডিকোডিং স্কিম সক্ষম করে যখন একটি বৃহৎ ক্ষমতার DRAM ডিভাইসকে নিম্ন শারীরিকভাবে সম্বোধন করা অঞ্চল জুড়ে বিভাজন করা হয়।

উদাহরণস্বরূপ, একটি 64GB DRAM অংশকে তিনটি অঞ্চলে উপ-বিভক্ত করা হয়েছে ঠিকানা অফসেটগুলি নিম্নোক্তভাবে হাই অর্ডার অ্যাড্রেস বিটে একটি সাধারণ বিয়োগ দ্বারা সঞ্চালিত:

| সারণি 6.42.1 ছিদ্র সহ 64GB DRAM পার্টিশনের উদাহরণ |

|||

|---|---|---|---|

| SoC-তে শারীরিক ঠিকানা | অফসেট | অভ্যন্তরীণ DRAM ঠিকানা | |

| 2 গিগাবাইট (32-বিট মানচিত্র) | 0x00 8000 0000 - 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 - 0x00 7FFF FFFF |

| 30 গিগাবাইট (36-বিট মানচিত্র) | 0x08 8000 0000 - 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 - 0x07 FFFF FFFF |

| 32 গিগাবাইট (40-বিট মানচিত্র) | 0x88 0000 0000 – 0x8F FFFF FFFF | -0x80 0000 0000 | 0x08 0000 0000 - 0x0F FFFF FFFF |

ARM CPU-র জন্য প্রস্তাবিত 44-বিট এবং 48-বিট ঠিকানাযুক্ত মেমরি মানচিত্র

অনুমান করুন যে একটি ব্যক্তিগত কম্পিউটারে 1024GB (= 1TB) মেমরি রয়েছে; এটি খুব বেশি স্মৃতি। আর তাই, 44-বিট এবং 48-বিট অ্যাড্রেসড মেমরি ম্যাপ ARM CPU-এর জন্য যথাক্রমে 16 TB এবং 256 TB, ভবিষ্যতের কম্পিউটারের প্রয়োজনের জন্য প্রস্তাবনা মাত্র। প্রকৃতপক্ষে, এআরএম সিপিইউগুলির জন্য এই প্রস্তাবগুলি পূর্ববর্তী মেমরি মানচিত্রের অনুপাত অনুসারে মেমরির একই বিভাজন অনুসরণ করে। সেটি হল: 50% DRAM এর মধ্যে একটি ঐচ্ছিক ছিদ্র, 25% ম্যাপ করা I/O স্পেস এবং সংরক্ষিত স্থান এবং বাকি 25% জায়গা আগের মেমরি ম্যাপের জন্য।

52-বিট, 56-বিট, 60-বিট এবং 64-বিট ঠিকানাযুক্ত মেমরি মানচিত্রগুলি এখনও সুদূর ভবিষ্যতের জন্য ARM 64 বিটের জন্য প্রস্তাবিত। সেই সময়ে বিজ্ঞানীরা যদি এখনও পুরো মেমরি স্পেসের 50 : 25 : 25 বিভাজন উপযোগী বলে মনে করেন তবে তারা অনুপাত বজায় রাখবেন।

বিঃদ্রঃ : SoC মানে সিস্টেম-অন-চিপ যা µP চিপের সার্কিটকে বোঝায় যা অন্যথায় থাকত না।

এসআরএএম বা স্ট্যাটিক র্যান্ডম অ্যাক্সেস মেমরি আরও প্রথাগত ডিআরএএম থেকে দ্রুত, তবে আরও সিলিকন এলাকা প্রয়োজন। SRAM এর রিফ্রেশ করার প্রয়োজন নেই। পাঠক RAM কে SRAM হিসাবে কল্পনা করতে পারেন।

6.43 ARM 64-এর জন্য অ্যাসেম্বলি ল্যাঙ্গুয়েজ অ্যাড্রেসিং মোড

এআরএম হল একটি লোড/স্টোর আর্কিটেকচার যার সাথে একটি গাণিতিক লজিক অপারেশনের মতো কোনো প্রক্রিয়াকরণের আগে মেমরি থেকে একটি প্রসেসর রেজিস্টারে ডেটা লোড করা প্রয়োজন। একটি পরবর্তী নির্দেশনা ফলাফলটিকে মেমরিতে ফিরিয়ে রাখে। যদিও এটি x86 এবং এর পরবর্তী x64 আর্কিটেকচার থেকে একধাপ পিছিয়ে বলে মনে হতে পারে, যা সরাসরি মেমরির অপারেন্ডগুলিতে একটি একক নির্দেশে কাজ করে, বাস্তবে, লোড/স্টোর পদ্ধতিটি উচ্চ গতিতে বেশ কয়েকটি ক্রমিক ক্রিয়াকলাপ সম্পাদন করার অনুমতি দেয়। একটি অপারেন্ড একবার এটি অনেকগুলি প্রসেসর রেজিস্টারের একটিতে লোড হয়ে গেলে।

এআরএম অ্যাসেম্বলি ভাষার বিন্যাস x64 (x86) সিরিজের সাথে মিল এবং পার্থক্য রয়েছে।

- অফসেট : একটি স্বাক্ষরিত ধ্রুবক বেস রেজিস্টারে যোগ করা যেতে পারে। অফসেট নির্দেশের অংশ হিসাবে টাইপ করা হয়. উদাহরণস্বরূপ: ldr x0, [rx, #10] r1+10 ঠিকানায় শব্দের সাথে r0 লোড করে।

- নিবন্ধন : একটি স্বাক্ষরবিহীন ইনক্রিমেন্ট যা একটি রেজিস্টারে সংরক্ষিত থাকে তা একটি বেস রেজিস্টারের মান থেকে যোগ বা বিয়োগ করা যেতে পারে। উদাহরণস্বরূপ: ldr r0, [x1, x2] x1+x2 ঠিকানায় শব্দের সাথে r0 লোড করে। যেকোন একটি রেজিস্টারকে বেস রেজিস্টার হিসেবে ভাবা যেতে পারে।

- স্কেলড রেজিস্টার : বেস রেজিস্টার মান থেকে যোগ বা বিয়োগ করার আগে একটি রেজিস্টারে একটি ইনক্রিমেন্ট একটি নির্দিষ্ট সংখ্যক বিট পজিশন দ্বারা বাম বা ডানে স্থানান্তরিত হয়। উদাহরণস্বরূপ: ldr x0, [x1, x2, lsl #3] r1+(r2×8) ঠিকানায় শব্দের সাথে r0 লোড করে। শিফটটি একটি লজিক্যাল বাম বা ডান শিফট (lsl বা lsr) হতে পারে যা খালি করা বিট পজিশনে শূন্য বিট সন্নিবেশ করায় অথবা একটি গাণিতিক ডান শিফট (asr) যা খালি অবস্থানে সাইন বিটের প্রতিলিপি করে।

যখন দুটি অপারেন্ড জড়িত থাকে, তখন গন্তব্যটি উৎসের আগে (বাম দিকে) আসে (এতে কিছু ব্যতিক্রম আছে)। ARM সমাবেশ ভাষার জন্য opcodes কেস সংবেদনশীল।

তাত্ক্ষণিক ARM64 অ্যাড্রেসিং মোড

উদাহরণ:

mov r0, #0xFF000000 ; 32-বিট মান FF000000h r0 এ লোড করুন

একটি দশমিক মান 0x ছাড়া কিন্তু এখনও # এর আগে আছে।

সরাসরি নিবন্ধন করুন

উদাহরণ:

mov x0, x1 ; x1 থেকে x0 কপি করুন

পরোক্ষ নিবন্ধন করুন

উদাহরণ:

str x0, [x3]; x3 ঠিকানায় x0 সংরক্ষণ করুন

অফসেটের সাথে পরোক্ষ নিবন্ধন করুন

উদাহরণ:

ldr x0, [x1, #32] ; ঠিকানায় মান সহ r0 লোড করুন [r1+32]; r1 হল বেস রেজিস্টার

str x0, [x1, #4] ; ঠিকানায় r0 সংরক্ষণ করুন [r1+4]; r1 হল বেস রেজিস্টার; সংখ্যা বেস 10

অফসেটের সাথে পরোক্ষ নিবন্ধন করুন (প্রাক-বর্ধিত)

উদাহরণ:

ldr x0, [x1, #32]! ; [r1+32] দিয়ে r0 লোড করুন এবং r1 তে (r1+32) আপডেট করুন

str x0, [x1, #4]! ; r0 থেকে [r1+4] সংরক্ষণ করুন এবং r1 থেকে (r1+4) আপডেট করুন

“!” এর ব্যবহার লক্ষ্য করুন। প্রতীক

অফসেটের সাথে পরোক্ষ নিবন্ধন করুন (পোস্ট-ইনক্রিমেন্টেড)

উদাহরণ:

ldr x0, [x1], #32 ; x0 এ [x1] লোড করুন, তারপর x1 তে (x1+32) আপডেট করুন

str x0, [x1], #4 ; x0 থেকে [x1] সঞ্চয় করুন, তারপর x1 থেকে (x1+4) আপডেট করুন

ডাবল রেজিস্টার পরোক্ষ

অপারেন্ডের ঠিকানা হল একটি বেস রেজিস্টার এবং একটি ইনক্রিমেন্ট রেজিস্টারের সমষ্টি। রেজিস্টারের নামগুলি বর্গাকার বন্ধনী দ্বারা বেষ্টিত।

উদাহরণ:

ldr x0, [x1, x2] ; [x1+x2] দিয়ে x0 লোড করুন

str x0, [rx, x2]; স্টোর x0 থেকে [x1+x2]

আপেক্ষিক ঠিকানা মোড

আপেক্ষিক অ্যাড্রেসিং মোডে, কার্যকর নির্দেশ হল প্রোগ্রাম কাউন্টারের পরবর্তী নির্দেশ, এবং একটি সূচক। সূচক ইতিবাচক বা নেতিবাচক হতে পারে।

উদাহরণ:

ldr x0, [pc, #24]

এর অর্থ হল লোড রেজিস্টার X0 শব্দটি যা PC বিষয়বস্তু প্লাস 24 দ্বারা নির্দেশিত।

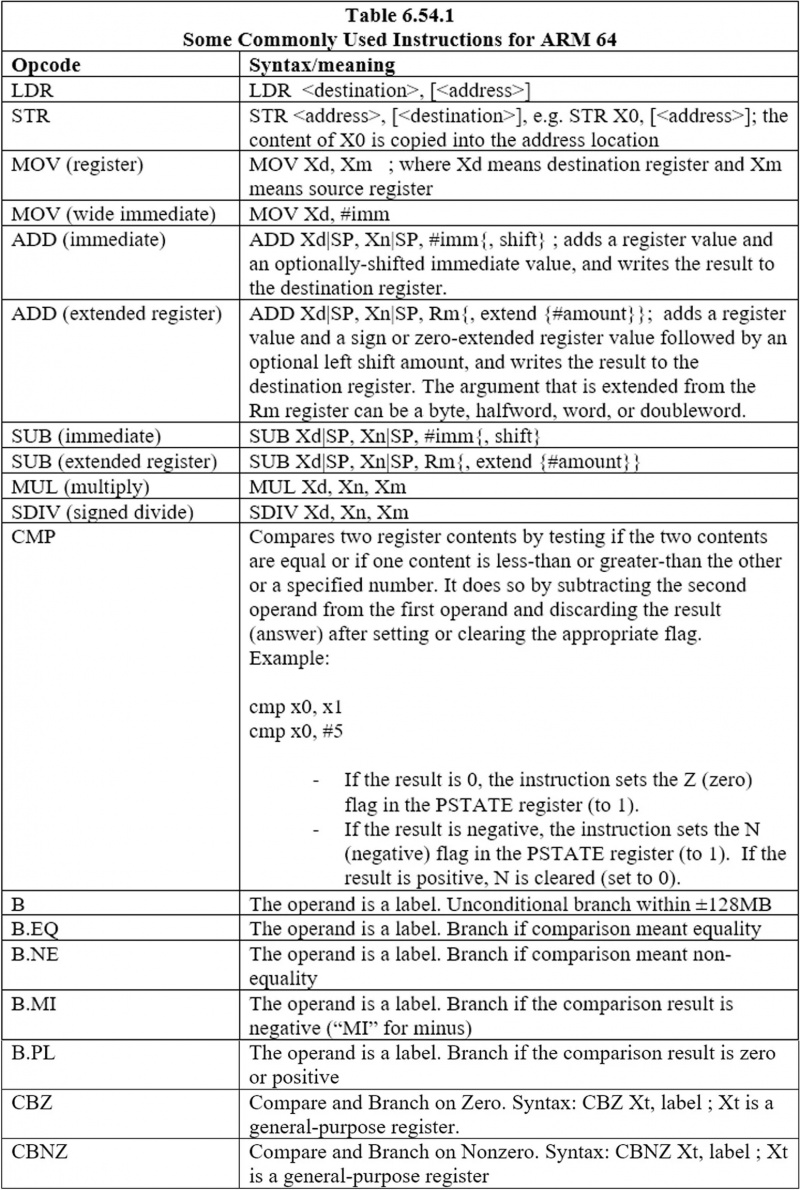

6.44 ARM 64 এর জন্য কিছু সাধারণভাবে ব্যবহৃত নির্দেশাবলী

এখানে সাধারণভাবে ব্যবহৃত নির্দেশাবলী রয়েছে:

6.45 লুপিং

চিত্রণ

নিচের কোডটি X10 রেজিস্টারে X9-এর মানের সাথে মান যোগ করতে থাকে যতক্ষণ না X8-এর মান শূন্য হয়। অনুমান করুন যে সমস্ত মান পূর্ণসংখ্যা। X8-এর মান প্রতিটি পুনরাবৃত্তিতে 1 দ্বারা বিয়োগ করা হয়:

লুপ:

CBZ X8, এড়িয়ে যান

X9, X9, X10 যোগ করুন; প্রথম X9 হল গন্তব্য এবং দ্বিতীয় X9 হল উৎস৷

SUB X8, X8, #1 ; প্রথম X8 হল গন্তব্য এবং দ্বিতীয় X8 হল উৎস৷

বি লুপ

এড়িয়ে যান:

6502 µP এবং X64 µP-এর মতো, ARM 64 µP-এর লেবেল লাইনের শুরুতে শুরু হয়। বাকি নির্দেশাবলী লাইনের শুরুর পরে কিছু স্পেসে শুরু হয়। x64 এবং ARM 64 এর সাথে, লেবেলটি একটি কোলন এবং একটি নতুন লাইন অনুসরণ করে। 6502 সহ, লেবেলটি একটি স্থানের পরে একটি নির্দেশ দ্বারা অনুসরণ করা হয়। পূর্ববর্তী কোডে, প্রথম নির্দেশ যা হল 'CBZ X8, Skip' এর অর্থ হল X8-এ মান যদি শূন্য হয়, তাহলে 'skip:' লেবেলে চালিয়ে যান, এর মধ্যে নির্দেশাবলী এড়িয়ে যান এবং নীচের বাকি নির্দেশাবলীর সাথে চালিয়ে যান 'এড়িয়ে যান:'। 'B লুপ' হল 'লুপ' লেবেলে একটি নিঃশর্ত লাফ। অন্য কোন লেবেল নাম 'লুপ' এর জায়গায় ব্যবহার করা যেতে পারে।

সুতরাং, 6502 µP-এর মতো, ARM 64-এর সাথে একটি লুপ পেতে শাখা নির্দেশাবলী ব্যবহার করুন।

6.46 ARM 64 ইনপুট/আউটপুট

সমস্ত ARM পেরিফেরাল (অভ্যন্তরীণ পোর্ট) মেমরি ম্যাপ করা হয়। এর মানে হল যে প্রোগ্রামিং ইন্টারফেস হল মেমরি অ্যাড্রেসড রেজিস্টারের একটি সেট (অভ্যন্তরীণ পোর্ট)। এই জাতীয় রেজিস্টারের ঠিকানা একটি নির্দিষ্ট মেমরি বেস ঠিকানা থেকে একটি অফসেট। এটি 6502 কীভাবে ইনপুট/আউটপুট করে তার অনুরূপ। ARM-এর আলাদা I/O ঠিকানা স্থানের বিকল্প নেই।

ARM 64 এর 6.47 স্ট্যাক

ARM 64-এর মেমরিতে একটি স্ট্যাক (RAM) রয়েছে যেভাবে 6502 এবং x64-এর রয়েছে। যাইহোক, ARM64 এর সাথে, কোন পুশ বা পপ অপকোড নেই। ARM 64-এর স্ট্যাকটিও নিচের দিকে বৃদ্ধি পায়। স্ট্যাক পয়েন্টারে ঠিকানাটি স্ট্যাকের মধ্যে রাখা শেষ মানের শেষ বাইটের ঠিক পরে পয়েন্ট করে।

ARM64 এর জন্য কোন জেনেরিক পপ বা পুশ অপকোড না থাকার কারণ হল যে ARM 64 তার স্ট্যাকটি পরপর 16 বাইটের গ্রুপে পরিচালনা করে। যাইহোক, মানগুলি এক বাইট, দুই বাইট, চার বাইট এবং 8 বাইটের বাইট গ্রুপে বিদ্যমান। সুতরাং, একটি মান স্ট্যাকের মধ্যে স্থাপন করা যেতে পারে, এবং 16 বাইটের জন্য বাকি স্থানগুলি (বাইট অবস্থানগুলি) ডামি বাইট দিয়ে প্যাড করা হয়। এতে স্মৃতিশক্তি নষ্ট হওয়ার অসুবিধা রয়েছে। একটি ভাল সমাধান হল ছোট মান দিয়ে 16-বাইটের অবস্থান পূরণ করা এবং কিছু প্রোগ্রামার লিখিত কোড রয়েছে যা 16-বাইট অবস্থানের মানগুলি কোথা থেকে এসেছে তা ট্র্যাক করে (রেজিস্টার)। এই অতিরিক্ত কোড মান ফিরে টানার প্রয়োজন. এর একটি বিকল্প হল দুটি 8-বাইটের সাধারণ উদ্দেশ্যের রেজিস্টারগুলিকে বিভিন্ন মান দিয়ে পূরণ করা, এবং তারপর দুটি 8-বাইট রেজিস্টারের বিষয়বস্তু একটি স্ট্যাকে পাঠানো। স্ট্যাকের মধ্যে যাওয়া এবং স্ট্যাক ছেড়ে যাওয়া নির্দিষ্ট ছোট মানগুলি ট্র্যাক করার জন্য একটি অতিরিক্ত কোড এখনও এখানে প্রয়োজন।

নিম্নলিখিত কোড স্ট্যাকের মধ্যে চারটি 4-বাইট ডেটা সঞ্চয় করে:

str w0, [sp, #-4]!

str w1, [sp, #-8]!

str w2, [sp, #-12]!

str w3, [sp, #-16]!

রেজিস্টারের প্রথম চারটি বাইট (w) - x0, x1, x2, এবং x3 - স্ট্যাকের মধ্যে 16-টানা বাইট অবস্থানে পাঠানো হয়। 'str' ব্যবহার লক্ষ্য করুন এবং 'পুশ' নয়। প্রতিটি নির্দেশের শেষে বিস্ময়বোধক চিহ্নটি নোট করুন। যেহেতু মেমরি স্ট্যাক নিচের দিকে বাড়তে থাকে, তাই প্রথম চার-বাইটের মান একটি অবস্থানে শুরু হয় যা আগের স্ট্যাক পয়েন্টার অবস্থানের নিচে মাইনাস-ফোর বাইট। বাকি চার বাইট মান অনুসরণ করে, নিচে যাচ্ছে। নিম্নলিখিত কোড সেগমেন্টটি চারটি বাইট পপ করার সমতুল্য সঠিক (এবং ক্রমে) করবে:

ldr w3, [sp], #0

ldr w2, [sp], #4

ldr w1, [sp], #8

ldr w0, [sp], #12

পপ এর পরিবর্তে ldr opcode ব্যবহার নোট করুন। এছাড়াও মনে রাখবেন এখানে বিস্ময়বোধক চিহ্ন ব্যবহার করা হয়নি।

X0 (8 বাইট) এবং X1 (8 বাইট) এর সমস্ত বাইট স্ট্যাকের 16 বাইট-অবস্থানে নিম্নরূপ পাঠানো যেতে পারে:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

এই ক্ষেত্রে, x2 (w2) এবং x3 (w3) রেজিস্টারের প্রয়োজন নেই। সমস্ত কাঙ্ক্ষিত বাইটগুলি X0 এবং X2 রেজিস্টারে রয়েছে। রেজিস্টার বিষয়বস্তুর জোড়া RAM এ সংরক্ষণ করার জন্য stp opcode নোট করুন। বিস্ময়বোধক চিহ্নটিও নোট করুন। পপ সমতুল্য হল:

ldp x0, x1, [sp], #0

এই নির্দেশের জন্য কোন বিস্ময়সূচক চিহ্ন নেই। মেমরি থেকে দুটি µP রেজিস্টারে পরপর দুটি ডেটা অবস্থান লোড করার জন্য LDR-এর পরিবর্তে opcode LDP নোট করুন। এছাড়াও মনে রাখবেন যে মেমরি থেকে একটি µP রেজিস্টারে অনুলিপি করা হচ্ছে লোড হচ্ছে, ডিস্ক থেকে RAM এ একটি ফাইল লোড করার সাথে বিভ্রান্ত হবেন না এবং একটি µP রেজিস্টার থেকে RAM এ অনুলিপি করা হচ্ছে সংরক্ষণ করা হচ্ছে।

6.48 সাবরুটিন

একটি সাবরুটিন হল কোডের একটি ব্লক যা একটি কাজ সম্পাদন করে, ঐচ্ছিকভাবে কিছু আর্গুমেন্টের উপর ভিত্তি করে এবং ঐচ্ছিকভাবে একটি ফলাফল প্রদান করে। নিয়ম অনুসারে, R0 থেকে R3 রেজিস্টার (চারটি রেজিস্টার) একটি সাবরুটিনে আর্গুমেন্ট (প্যারামিটার) পাস করার জন্য ব্যবহার করা হয়, এবং R0 একটি ফলাফল কলারের কাছে ফেরত দেওয়ার জন্য ব্যবহার করা হয়। একটি সাবরুটিন যার জন্য 4টির বেশি ইনপুট প্রয়োজন অতিরিক্ত ইনপুটগুলির জন্য স্ট্যাক ব্যবহার করে। একটি সাবরুটিন কল করতে, লিঙ্ক বা শর্তাধীন শাখা নির্দেশনা ব্যবহার করুন। লিঙ্ক নির্দেশের জন্য সিনট্যাক্স হল:

BL লেবেল

যেখানে BL হল opcode এবং লেবেল সাবরুটিনের শুরু (ঠিকানা) প্রতিনিধিত্ব করে। এই শাখাটি শর্তহীন, 128MB এর মধ্যে সামনের দিকে বা পিছনের দিকে। শর্তসাপেক্ষ শাখা নির্দেশের জন্য সিনট্যাক্স হল:

B.cond লেবেল

যেখানে cond শর্ত, যেমন, eq (সমান) বা ne (সমান নয়)। নিম্নলিখিত প্রোগ্রামটিতে doadd সাবরুটিন রয়েছে যা দুটি আর্গুমেন্টের মান যোগ করে এবং R0 তে ফলাফল প্রদান করে:

এরিয়া সাবরাউট, কোড, READONLY ; কোডের এই ব্লকের নাম দিন

প্রবেশ; কার্যকর করার জন্য প্রথম নির্দেশ চিহ্নিত করুন

MOV r0, #10 শুরু করুন; পরামিতি সেট আপ করুন

MOV r1, #3

BL doadd; সাবরুটিন কল করুন

MOV r0, #0x18 বন্ধ করুন; angel_SWIreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_Application Exit

SVC #0x123456 ; এআরএম সেমিহোস্টিং (পূর্বে SWI)

doadd ADD r0, r0, r1 ; সাবরুটিন কোড

বিএক্স এলআর; সাবরুটিন থেকে ফিরে

;

শেষ ; ফাইলের শেষ চিহ্নিত করুন

যোগ করার জন্য সংখ্যাগুলি হল দশমিক 10 এবং দশমিক 3। কোডের এই ব্লকের (প্রোগ্রাম) প্রথম দুটি লাইন পরে ব্যাখ্যা করা হবে। পরের তিনটি লাইন 10 থেকে R0 রেজিস্টার এবং 3 থেকে R1 রেজিস্টার পাঠায় এবং doadd সাবরুটিনকেও কল করে। 'doadd' হল সেই লেবেল যা সাবরুটিনের শুরুর ঠিকানা ধারণ করে।

সাবরুটিন মাত্র দুটি লাইন নিয়ে গঠিত। প্রথম লাইনটি R0 এর 10 বিষয়বস্তুর সাথে R-এর বিষয়বস্তু 3 যোগ করে যা R0-এ 13-এর ফলাফলের অনুমতি দেয়। BX অপকোড এবং LR অপারেন্ড সহ দ্বিতীয় লাইনটি সাবরুটিন থেকে কলার কোডে ফিরে আসে।

ডান

ARM 64-এ RET opcode এখনও সাবরুটিনের সাথে ডিল করে, কিন্তু 6502-এ RTS বা x64-এ RET, বা ARM 64-এ 'BX LR' সংমিশ্রণ থেকে ভিন্নভাবে কাজ করে। ARM 64-এ, RET-এর সিনট্যাক্স হল:

সোজা {Xn}

এই নির্দেশটি প্রোগ্রামটিকে একটি সাবরুটিন দিয়ে চালিয়ে যাওয়ার সুযোগ দেয় যা কলার সাবরুটিন নয়, অথবা অন্য কিছু নির্দেশ এবং এর নিম্নলিখিত কোড সেগমেন্ট দিয়ে চালিয়ে যেতে পারে। Xn হল একটি সাধারণ-উদ্দেশ্য রেজিস্টার যেখানে প্রোগ্রামটি চালিয়ে যাওয়া উচিত এমন ঠিকানা ধারণ করে। এই নির্দেশ নিঃশর্ত শাখা. Xn না দিলে এটি X30-এর বিষয়বস্তুতে ডিফল্ট হয়।

পদ্ধতি কল স্ট্যান্ডার্ড

যদি প্রোগ্রামার চান যে তার কোড অন্য কারো দ্বারা লিখিত কোডের সাথে বা কম্পাইলার দ্বারা উত্পাদিত কোডের সাথে ইন্টারঅ্যাক্ট করতে, প্রোগ্রামারকে সেই ব্যক্তি বা কম্পাইলার লেখকের সাথে রেজিস্টার ব্যবহারের নিয়মগুলির সাথে একমত হতে হবে। এআরএম আর্কিটেকচারের জন্য, এই নিয়মগুলিকে প্রসিডিউর কল স্ট্যান্ডার্ড বা পিসিএস বলা হয়। এগুলো দুই বা তিন পক্ষের মধ্যে চুক্তি। পিসিএস নিম্নলিখিতগুলি নির্দিষ্ট করে:

- কোন µP রেজিস্টারগুলি ফাংশনে (সাবরুটিন) আর্গুমেন্টগুলি পাস করতে ব্যবহৃত হয়

- কোন µP রেজিস্টার ব্যবহার করা হয় ফলাফলকে সেই ফাংশনে ফেরাতে যা কলিং করে যা কলকারী নামে পরিচিত

- কোন µP কল করা ফাংশনটিকে নিবন্ধন করে, যা callee নামে পরিচিত, তা বিকৃত করতে পারে

- যা µP নিবন্ধন করে কলকারী দুর্নীতি করতে পারে না

6.49 বাধা

এআরএম প্রসেসরের জন্য দুটি ধরণের ইন্টারাপ্ট কন্ট্রোলার সার্কিট উপলব্ধ রয়েছে:

- স্ট্যান্ডার্ড ইন্টারাপ্ট কন্ট্রোলার: ইন্টারাপ্ট কন্ট্রোলারে একটি ডিভাইস বিটম্যাপ রেজিস্টার পড়ে কোন ডিভাইসের সার্ভিসিং প্রয়োজন তা ইন্টারাপ্ট হ্যান্ডলার নির্ধারণ করে।

- ভেক্টর ইন্টারাপ্ট কন্ট্রোলার (ভিআইসি): বাধাগুলিকে অগ্রাধিকার দেয় এবং কোন ডিভাইসটি বাধা সৃষ্টি করেছে তা নির্ধারণকে সহজ করে। প্রতিটি বিঘ্নের সাথে একটি অগ্রাধিকার এবং একটি হ্যান্ডলার ঠিকানা সংযুক্ত করার পরে, VIC শুধুমাত্র প্রসেসরকে একটি বাধা সংকেত প্রদান করে যদি একটি নতুন বাধার অগ্রাধিকার বর্তমানে কার্যকর করা ইন্টারাপ্ট হ্যান্ডলারের চেয়ে বেশি হয়।

বিঃদ্রঃ : ব্যতিক্রম ত্রুটি বোঝায়। 32-বিট এআরএম কম্পিউটারের জন্য ভেক্টর ইন্টারাপ্ট কন্ট্রোলারের বিবরণ নিম্নরূপ (64 বিট অনুরূপ):

| সারণি 6.49.1 32-বিট কম্পিউটারের জন্য ARM ভেক্টর ব্যতিক্রম/ইন্টারপ্ট |

|||

|---|---|---|---|

| ব্যতিক্রম/বিঘ্ন | ছোট হাত | ঠিকানা | উচ্চ ঠিকানা |

| রিসেট | রিসেট | 0x00000000 | 0xffff0000 |

| অনির্ধারিত নির্দেশ | ইউএনডিইএফ | 0x00000004 | 0xffff0004 |

| সফ্টওয়্যার বাধা | SWI | 0x00000008 | 0xffff0008 |

| প্রিফেচ অ্যাবোর্ট | pabt | 0x0000000C | 0xffff000C |

| গর্ভপাতের তারিখ | DABT | 0x00000010 | 0xffff0010 |

| সংরক্ষিত | - | 0x00000014 | 0xffff0014 |

| বিঘ্নিত অনুরোধ | আইআরকিউ | 0x00000018 | 0xffff0018 |

| দ্রুত বাধা অনুরোধ | FIQ | 0x0000001C | 0xffff001C |

এই 6502 স্থাপত্যের জন্য ব্যবস্থা মত দেখায় যেখানে এনএমআই , বি.আর , এবং আইআরকিউ পৃষ্ঠা জিরোতে পয়েন্টার থাকতে পারে, এবং সংশ্লিষ্ট রুটিনগুলি মেমরিতে বেশি (ROM OS)। পূর্ববর্তী টেবিলের সারিগুলির সংক্ষিপ্ত বিবরণ নিম্নরূপ:

রিসেট

প্রসেসর পাওয়ার আপ হলে এটি ঘটে। এটি সিস্টেম শুরু করে এবং বিভিন্ন প্রসেসর মোডের জন্য স্ট্যাক সেট আপ করে। এটি সর্বোচ্চ অগ্রাধিকারের ব্যতিক্রম। রিসেট হ্যান্ডলারে প্রবেশ করার পরে, CPSR SVC মোডে থাকে এবং IRQ এবং FIQ উভয় বিটই 1 এ সেট করা হয়, যেকোনো বাধাকে মাস্ক করে।

গর্ভপাতের তারিখ

দ্বিতীয় সর্বোচ্চ অগ্রাধিকার। এটি ঘটে যখন আমরা একটি অবৈধ ঠিকানায় পড়ার/লেখার চেষ্টা করি বা ভুল অ্যাক্সেসের অনুমতি অ্যাক্সেস করি। ডেটা অ্যাবোর্ট হ্যান্ডলারে প্রবেশ করার পরে, IRQs নিষ্ক্রিয় করা হবে (আই-বিট সেট 1) এবং FIQ সক্রিয় করা হবে। আইআরকিউগুলি মুখোশযুক্ত, তবে এফআইকিউগুলি মুখোশহীন রাখা হয়।

FIQ

সর্বোচ্চ অগ্রাধিকার বাধা, IRQ এবং FIQ, FIQ পরিচালনা না করা পর্যন্ত নিষ্ক্রিয় করা হয়।

আইআরকিউ

উচ্চ অগ্রাধিকার বিঘ্ন, IRQ হ্যান্ডলার, শুধুমাত্র যদি কোন চলমান FIQ এবং ডেটা বাতিল না থাকে তাহলে প্রবেশ করানো হয়।

প্রি-ফেচ অ্যাবোর্ট

এটি ডেটা বাতিলের অনুরূপ কিন্তু ঠিকানা আনয়ন ব্যর্থতায় ঘটে। হ্যান্ডলারে প্রবেশ করার পরে, IRQs নিষ্ক্রিয় করা হয় কিন্তু FIQ গুলি সক্রিয় থাকে এবং একটি প্রি-ফেচ অ্যাবোর্টের সময় ঘটতে পারে।

SWI

একটি সফ্টওয়্যার ইন্টারাপ্ট (SWI) ব্যতিক্রম ঘটে যখন SWI নির্দেশ কার্যকর করা হয় এবং অন্যান্য উচ্চ-অগ্রাধিকারের ব্যতিক্রমগুলির কোনোটিই পতাকাঙ্কিত করা হয়নি।

অনির্ধারিত নির্দেশ

অনির্ধারিত নির্দেশের ব্যতিক্রম ঘটে যখন একটি নির্দেশনা যা ARM বা থাম্ব নির্দেশনা সেটে নেই তা পাইপলাইনের কার্যকরী পর্যায়ে পৌঁছে এবং অন্য কোনো ব্যতিক্রমকে পতাকাঙ্কিত করা হয়নি। এটি SWI-এর মতো একই অগ্রাধিকার যেমন এক সময়ে ঘটতে পারে৷ এর মানে হল যে নির্দেশটি কার্যকর করা হচ্ছে তা একই সময়ে একটি SWI নির্দেশ এবং একটি অনির্ধারিত নির্দেশ উভয়ই হতে পারে না।

এআরএম ব্যতিক্রম হ্যান্ডলিং

নিম্নলিখিত ঘটনাগুলি ঘটে যখন একটি ব্যতিক্রম ঘটে:

- ব্যতিক্রম মোডের SPSR-এ CPSR সংরক্ষণ করুন।

- পিসি ব্যতিক্রম মোডের LR এ সংরক্ষণ করা হয়।

- লিংক রেজিস্টার বর্তমান নির্দেশের উপর ভিত্তি করে একটি নির্দিষ্ট ঠিকানায় সেট করা হয়েছে। উদাহরণ স্বরূপ: ISR, LR = শেষ সম্পাদিত নির্দেশ + 8 এর জন্য।

- ব্যতিক্রম সম্পর্কে CPSR আপডেট করুন।

- ব্যতিক্রম হ্যান্ডলারের ঠিকানায় পিসি সেট করুন।

6.5 নির্দেশাবলী এবং ডেটা

ডেটা ভেরিয়েবল (তাদের মান সহ লেবেল) এবং অ্যারে এবং অ্যারের অনুরূপ অন্যান্য কাঠামোকে বোঝায়। স্ট্রিং অক্ষর একটি অ্যারের মত. পূর্ববর্তী অধ্যায়ের একটিতে পূর্ণসংখ্যার একটি অ্যারে দেখা যায়। নির্দেশাবলী অপকোড এবং তাদের অপারেন্ড উল্লেখ করে। মেমরির একটি অবিরত বিভাগে মিশ্রিত অপকোড এবং ডেটা দিয়ে একটি প্রোগ্রাম লেখা যেতে পারে। এই পদ্ধতির অসুবিধা আছে কিন্তু সুপারিশ করা হয় না।

একটি প্রোগ্রাম প্রথমে নির্দেশাবলী সহ লিখতে হবে, তারপরে ডেটা (ডেটামের বহুবচন হল ডেটা)। নির্দেশাবলী এবং ডেটার মধ্যে বিচ্ছেদ মাত্র কয়েক বাইট হতে পারে। একটি প্রোগ্রামের জন্য, নির্দেশাবলী এবং ডেটা উভয়ই মেমরিতে এক বা দুটি পৃথক বিভাগে থাকতে পারে।

6.6 হার্ভার্ড আর্কিটেকচার

প্রারম্ভিক কম্পিউটারগুলির মধ্যে একটিকে হার্ভার্ড মার্ক I (1944) বলা হয়। একটি কঠোর হার্ভার্ড আর্কিটেকচার প্রোগ্রাম নির্দেশাবলীর জন্য একটি ঠিকানা স্থান এবং ডেটার জন্য একটি পৃথক পৃথক ঠিকানা স্থান ব্যবহার করে। এর মানে হল দুটি আলাদা স্মৃতি আছে। নিম্নলিখিত স্থাপত্য দেখায়:

চিত্র 6.71 হার্ভার্ড আর্কিটেকচার

কন্ট্রোল ইউনিট নির্দেশনা ডিকোডিং করে। অ্যারিথমেটিক লজিক ইউনিট (এএলইউ) কম্বিনেশনাল লজিক (গেট) দিয়ে গাণিতিক ক্রিয়াকলাপ করে। ALU লজিক্যাল ক্রিয়াকলাপও করে (যেমন স্থানান্তর)।

6502 মাইক্রোপ্রসেসরের সাথে, একটি নির্দেশনা প্রথমে মাইক্রোপ্রসেসরে (নিয়ন্ত্রণ ইউনিট) যায় তার আগে ডেটাম (ডেটার জন্য একক) তারা ইন্টারঅ্যাক্ট করার আগে µP রেজিস্টারে যায়। এটির জন্য কমপক্ষে দুটি ঘড়ির স্পন্দন প্রয়োজন এবং এটি নির্দেশাবলী এবং ডেটামের একযোগে অ্যাক্সেস নয়। অন্যদিকে, হার্ভার্ড আর্কিটেকচার নির্দেশাবলী এবং ডেটাতে একযোগে অ্যাক্সেস প্রদান করে, নির্দেশনা এবং ডেটাম উভয়ই একই সময়ে µP-এ প্রবেশ করে (অপকোড টু কন্ট্রোল ইউনিট এবং ডেটাম থেকে µP রেজিস্টার), কমপক্ষে একটি ঘড়ির পালস সংরক্ষণ করে। এটি সমান্তরালতার একটি রূপ। আধুনিক মাদারবোর্ডের হার্ডওয়্যার ক্যাশে সমান্তরালতার এই রূপটি ব্যবহার করা হয় (নিম্নলিখিত আলোচনা পড়ুন)।

6.7 ক্যাশে মেমরি

ক্যাশে মেমরি (RAM) হল একটি উচ্চ-গতির মেমরি অঞ্চল (প্রধান মেমরির গতির তুলনায়) যা অস্থায়ীভাবে ভবিষ্যতে ব্যবহারের জন্য প্রোগ্রাম নির্দেশাবলী বা ডেটা সংরক্ষণ করে। ক্যাশে মেমরি প্রধান মেমরির চেয়ে দ্রুত কাজ করে। সাধারণত, এই নির্দেশাবলী বা ডেটা আইটেমগুলি সাম্প্রতিক প্রধান মেমরি থেকে পুনরুদ্ধার করা হয় এবং শীঘ্রই আবার প্রয়োজন হতে পারে। ক্যাশে মেমরির প্রাথমিক উদ্দেশ্য হল একই প্রধান মেমরির অবস্থানগুলিতে বারবার অ্যাক্সেস করার গতি বাড়ানো। কার্যকর হওয়ার জন্য, ক্যাশে করা আইটেমগুলি অ্যাক্সেস করা অবশ্যই নির্দেশাবলী বা ডেটার মূল উত্স অ্যাক্সেস করার চেয়ে উল্লেখযোগ্যভাবে দ্রুত হতে হবে যাকে ব্যাকিং স্টোর হিসাবে উল্লেখ করা হয়৷

যখন ক্যাশিং ব্যবহার করা হয়, একটি প্রধান মেমরি অবস্থান অ্যাক্সেস করার প্রতিটি প্রচেষ্টা ক্যাশে অনুসন্ধানের সাথে শুরু হয়। অনুরোধ করা আইটেমটি উপস্থিত থাকলে, প্রসেসর পুনরুদ্ধার করে এবং অবিলম্বে এটি ব্যবহার করে। একে ক্যাশে হিট বলা হয়। যদি ক্যাশে অনুসন্ধান ব্যর্থ হয় (একটি ক্যাশে মিস), নির্দেশ বা ডেটা আইটেম ব্যাকিং স্টোর (প্রধান মেমরি) থেকে পুনরুদ্ধার করা আবশ্যক। অনুরোধ করা আইটেমটি পুনরুদ্ধার করার প্রক্রিয়াতে, একটি অনুলিপি ক্যাশে যুক্ত করা হয় একটি প্রত্যাশিত নিকট ভবিষ্যতে ব্যবহারের জন্য।

মেমরি ম্যানেজমেন্ট ইউনিট

মেমরি ম্যানেজমেন্ট ইউনিট (MMU) হল একটি সার্কিট যা মাদারবোর্ডে প্রধান মেমরি এবং সম্পর্কিত মেমরি রেজিস্টার পরিচালনা করে। অতীতে, এটি মাদারবোর্ডে একটি পৃথক সমন্বিত সার্কিট ছিল; কিন্তু আজ, এটি সাধারণত মাইক্রোপ্রসেসরের অংশ। MMU কে ক্যাশে (সার্কিট) পরিচালনা করা উচিত যা আজ মাইক্রোপ্রসেসরের একটি অংশ। ক্যাশে সার্কিট অতীতে একটি পৃথক সমন্বিত সার্কিট।

স্ট্যাটিক RAM

স্ট্যাটিক RAM (SRAM) এর DRAM এর তুলনায় যথেষ্ট দ্রুত অ্যাক্সেসের সময় রয়েছে, যদিও উল্লেখযোগ্যভাবে আরও জটিল সার্কিটরির খরচে। এসআরএএম বিট সেলগুলি সমন্বিত সার্কিট ডাইতে একটি ডিআরএএম ডিভাইসের কোষগুলির তুলনায় অনেক বেশি জায়গা নেয় যা সমপরিমাণ ডেটা সংরক্ষণ করতে সক্ষম। প্রধান মেমরি (RAM) সাধারণত DRAM (ডাইনামিক RAM) নিয়ে গঠিত।

ক্যাশে মেমরি কম্পিউটারের কর্মক্ষমতা উন্নত করে কারণ অনেক অ্যালগরিদম যা অপারেটিং সিস্টেম এবং অ্যাপ্লিকেশন দ্বারা সঞ্চালিত হয় রেফারেন্সের স্থানীয়তা প্রদর্শন করে। রেফারেন্সের স্থানীয়তা সম্প্রতি অ্যাক্সেস করা ডেটার পুনঃব্যবহারকে বোঝায়। এটিকে টেম্পোরাল লোক্যালিটি বলা হয়। একটি আধুনিক মাদারবোর্ডে, ক্যাশে মেমরি মাইক্রোপ্রসেসরের মতো একই ইন্টিগ্রেটেড সার্কিটে থাকে। প্রধান মেমরি (DRAM) অনেক দূরে এবং বাসের মাধ্যমে অ্যাক্সেসযোগ্য। রেফারেন্সের এলাকাটি স্থানিক লোকালয়কেও বোঝায়। স্থানিক লোকালয়টি শারীরিক নৈকট্যের কারণে ডেটা অ্যাক্সেসের উচ্চ গতির সাথে সম্পর্কযুক্ত।

একটি নিয়ম হিসাবে, ক্যাশে মেমরি অঞ্চলগুলি ব্যাকিং স্টোরের (প্রধান মেমরি) তুলনায় ছোট (বাইট অবস্থানের সংখ্যায়)। ক্যাশে মেমরি ডিভাইসগুলি সর্বাধিক গতির জন্য ডিজাইন করা হয়েছে যার অর্থ সাধারণত ব্যাকিং স্টোরে ব্যবহৃত ডেটা স্টোরেজ প্রযুক্তির তুলনায় এগুলি আরও জটিল এবং ব্যয়বহুল। তাদের সীমিত আকারের কারণে, ক্যাশে মেমরি ডিভাইসগুলি দ্রুত পূরণ করতে থাকে। যখন একটি ক্যাশে একটি নতুন এন্ট্রি সংরক্ষণ করার জন্য একটি উপলব্ধ অবস্থান নেই, একটি পুরানো এন্ট্রি বাতিল করা আবশ্যক. নতুন এন্ট্রি দ্বারা কোন ক্যাশে এন্ট্রি ওভাররাইট করা হবে তা নির্বাচন করতে ক্যাশে কন্ট্রোলার একটি ক্যাশে প্রতিস্থাপন নীতি ব্যবহার করে।

মাইক্রোপ্রসেসর ক্যাশে মেমরির লক্ষ্য হল সময়ের সাথে সাথে ক্যাশে হিটের শতাংশকে সর্বাধিক করা, এইভাবে নির্দেশনা কার্যকর করার সর্বোচ্চ টেকসই হার প্রদান করে। এই উদ্দেশ্য অর্জনের জন্য, ক্যাশিং লজিক অবশ্যই নির্ধারণ করবে কোন নির্দেশাবলী এবং ডেটা ক্যাশে স্থাপন করা হবে এবং নিকট ভবিষ্যতে ব্যবহারের জন্য ধরে রাখা হবে।

একটি প্রসেসরের ক্যাশিং লজিকের নিশ্চয়তা নেই যে একটি ক্যাশ করা ডেটা আইটেম একবার ক্যাশে ঢোকানোর পরে আবার ব্যবহার করা হবে।

ক্যাশিং এর যুক্তি এই সম্ভাবনার উপর নির্ভর করে যে টেম্পোরাল (সময়ের সাথে পুনরাবৃত্তি) এবং স্থানিক (স্পেস) লোকেলিটির কারণে, অদূর ভবিষ্যতে ক্যাশে করা ডেটা অ্যাক্সেস করার খুব ভাল সম্ভাবনা রয়েছে। আধুনিক প্রসেসরের ব্যবহারিক বাস্তবায়নে, ক্যাশে হিটগুলি সাধারণত 95 থেকে 97 শতাংশ মেমরি অ্যাক্সেসে ঘটে। যেহেতু ক্যাশে মেমরির লেটেন্সি DRAM-এর লেটেন্সির একটি ছোট ভগ্নাংশ, তাই একটি উচ্চ ক্যাশে হিট রেট ক্যাশে-মুক্ত ডিজাইনের তুলনায় একটি উল্লেখযোগ্য কর্মক্ষমতা উন্নতির দিকে নিয়ে যায়।

ক্যাশের সাথে কিছু সমান্তরালতা

পূর্বে উল্লিখিত হিসাবে, মেমরির একটি ভাল প্রোগ্রামের নির্দেশাবলী ডেটা থেকে আলাদা করা থাকে। কিছু ক্যাশে সিস্টেমে, প্রসেসরের 'বামে' একটি ক্যাশে সার্কিট থাকে এবং প্রসেসরের 'ডান' দিকে আরেকটি ক্যাশে সার্কিট থাকে। বাম ক্যাশে একটি প্রোগ্রামের (বা অ্যাপ্লিকেশন) নির্দেশাবলী পরিচালনা করে এবং ডান ক্যাশে একই প্রোগ্রামের (বা একই অ্যাপ্লিকেশন) ডেটা পরিচালনা করে। এটি একটি ভাল বৃদ্ধি গতি বাড়ে.

6.8 প্রসেস এবং থ্রেড

CISC এবং RISC উভয় কম্পিউটারেই প্রসেস আছে। সফ্টওয়্যারটিতে একটি প্রক্রিয়া চলছে। একটি প্রোগ্রাম যা চলমান (নির্বাহ করা) একটি প্রক্রিয়া। অপারেটিং সিস্টেম তার নিজস্ব প্রোগ্রাম সঙ্গে আসে. কম্পিউটার কাজ করার সময়, অপারেটিং সিস্টেমের প্রোগ্রামগুলি যা কম্পিউটারকে কাজ করতে সক্ষম করে সেগুলিও চলছে। এগুলো অপারেটিং সিস্টেমের প্রক্রিয়া। ব্যবহারকারী বা প্রোগ্রামার তার নিজের প্রোগ্রাম লিখতে পারেন. যখন ব্যবহারকারীর প্রোগ্রাম চলছে, এটি একটি প্রক্রিয়া। প্রোগ্রামটি অ্যাসেম্বলি ল্যাঙ্গুয়েজ বা সি বা সি++ এর মতো উচ্চ-স্তরের ভাষায় লেখা কিনা তা বিবেচ্য নয়। সমস্ত প্রক্রিয়া (ব্যবহারকারী বা ওএস) একটি 'শিডিউলার' নামক আরেকটি প্রক্রিয়া দ্বারা পরিচালিত হয়।

একটি থ্রেড একটি প্রক্রিয়ার অন্তর্গত একটি উপ-প্রক্রিয়ার মতো। একটি প্রক্রিয়া শুরু হতে পারে এবং থ্রেডে বিভক্ত হতে পারে এবং তারপরও একটি প্রক্রিয়া হিসাবে চলতে থাকে। থ্রেড ছাড়া একটি প্রক্রিয়া প্রধান থ্রেড হিসাবে বিবেচনা করা যেতে পারে। প্রক্রিয়া এবং তাদের থ্রেড একই সময়সূচী দ্বারা পরিচালিত হয়. সময়সূচী নিজেই একটি প্রোগ্রাম যখন এটি OS ডিস্কের বাসিন্দা হয়। মেমরিতে চলার সময়, সময়সূচী একটি প্রক্রিয়া।

6.9 মাল্টিপ্রসেসিং

থ্রেড প্রায় প্রক্রিয়া মত পরিচালিত হয়. মাল্টিপ্রসেসিং মানে একই সময়ে একাধিক প্রক্রিয়া চালানো। শুধুমাত্র একটি মাইক্রোপ্রসেসর সহ কম্পিউটার আছে। একাধিক মাইক্রোপ্রসেসর সহ কম্পিউটার রয়েছে। একটি একক মাইক্রোপ্রসেসরের সাথে, প্রক্রিয়াগুলি এবং/অথবা থ্রেডগুলি একই মাইক্রোপ্রসেসরকে ইন্টারলিভিং (বা টাইম-স্লাইসিং) পদ্ধতিতে ব্যবহার করে। এর মানে হল যে একটি প্রক্রিয়া প্রসেসর ব্যবহার করে এবং শেষ না করেই থেমে যায়। আরেকটি প্রক্রিয়া বা থ্রেড প্রসেসর ব্যবহার করে এবং শেষ না করেই থেমে যায়। তারপরে, অন্য একটি প্রক্রিয়া বা থ্রেড মাইক্রোপ্রসেসর ব্যবহার করে এবং শেষ না করেই থেমে যায়। এটি চলতে থাকে যতক্ষণ না সময়সূচী দ্বারা সারিবদ্ধ সমস্ত প্রক্রিয়া এবং থ্রেডগুলিতে প্রসেসরের একটি অংশ থাকে। এটিকে সমসাময়িক মাল্টিপ্রসেসিং বলা হয়।

যখন একাধিক মাইক্রোপ্রসেসর থাকে, তখন সমান্তরাল মাল্টিপ্রসেসিং হয়, একত্রিতার বিপরীতে। এই ক্ষেত্রে, প্রতিটি প্রসেসর একটি নির্দিষ্ট প্রক্রিয়া বা থ্রেড চালায়, অন্য প্রসেসর যা চলছে তার থেকে আলাদা। একই মাদারবোর্ডের সমস্ত প্রসেসর একই সময়ে সমান্তরাল মাল্টিপ্রসেসিংয়ে তাদের বিভিন্ন প্রক্রিয়া এবং/অথবা ভিন্ন থ্রেড চালায়। সমান্তরাল মাল্টিপ্রসেসিংয়ের প্রক্রিয়া এবং থ্রেডগুলি এখনও শিডিউলারের দ্বারা পরিচালিত হয়। সমান্তরাল মাল্টিপ্রসেসিং সমসাময়িক মাল্টিপ্রসেসিংয়ের চেয়ে দ্রুত।

এই মুহুর্তে, পাঠক আশ্চর্য হতে পারে যে সমান্তরাল প্রক্রিয়াকরণ সমসাময়িক প্রক্রিয়াকরণের চেয়ে দ্রুততর। কারণ প্রসেসর একই মেমরি এবং ইনপুট/আউটপুট পোর্ট শেয়ার করে (বিভিন্ন সময়ে ব্যবহার করতে হয়)। ওয়েল, ক্যাশে ব্যবহারের সাথে, মাদারবোর্ডের সামগ্রিক অপারেশন দ্রুততর হয়।

6.10 পেজিং

মেমরি ম্যানেজমেন্ট ইউনিট (MMU) হল একটি সার্কিট যা মাইক্রোপ্রসেসরের কাছাকাছি বা মাইক্রোপ্রসেসর চিপে থাকে। এটি মেমরি ম্যাপ বা পেজিং এবং অন্যান্য মেমরি সমস্যা পরিচালনা করে। 6502 µP বা কমোডোর-64 কম্পিউটারের কোনোটিতেই একটি MMU নেই (যদিও কমডোর-64-এ এখনও কিছু মেমরি ব্যবস্থাপনা রয়েছে)। কমডোর-64 মেমরি পরিচালনা করে পেজিং করে যেখানে প্রতিটি পৃষ্ঠা 256 10 বাইট দীর্ঘ (100 16 বাইট দীর্ঘ)। পেজিং করে স্মৃতি সামলাতে বাধ্য ছিল না। এটিতে এখনও কেবল একটি মেমরি মানচিত্র থাকতে পারে এবং তারপরে এমন প্রোগ্রামগুলি থাকতে পারে যা তাদের বিভিন্ন মনোনীত অঞ্চলে নিজেকে ফিট করে। ঠিক আছে, পেজিং হল মেমরির একটি দক্ষ ব্যবহার প্রদানের একটি উপায় যেখানে অনেক মেমরি বিভাগ নেই যেখানে একটি ডেটা বা প্রোগ্রাম থাকতে পারে না।

x86 386 কম্পিউটার আর্কিটেকচারটি 1985 সালে প্রকাশিত হয়েছিল। ঠিকানা বাসটি 32-বিট প্রশস্ত। সুতরাং, মোট 2 32 = 4,294,967,296 ঠিকানা স্থান সম্ভব। এই ঠিকানা স্থানটি 1,048,576 পৃষ্ঠা = 1,024 KB পৃষ্ঠাগুলিতে বিভক্ত। এই সংখ্যার পৃষ্ঠাগুলির সাথে, একটি পৃষ্ঠা 4,096 বাইট = 4 KB নিয়ে গঠিত। নিচের টেবিলটি x86 32-বিট আর্কিটেকচারের জন্য প্রকৃত ঠিকানা পৃষ্ঠাগুলি দেখায়:

| সারণি 6.10.1 x86 আর্কিটেকচারের জন্য ভৌত ঠিকানাযোগ্য পৃষ্ঠা |

||

|---|---|---|

| বেস 16 ঠিকানা | পাতা | বেস 10 ঠিকানা |

| FFFFF000 - FFFFFFFF | পৃষ্ঠা 1,048,575 | 4,294,963,200 - 4,294,967,295 |

| FFFFE000 - FFFFEFFF | পৃষ্ঠা 1,044,479 | 4,294,959,104 - 4,294,963,199 |

| FFFFD000 - FFFFDFFF | পৃষ্ঠা 1,040,383 | 4,294,955,008 - 4,294,959,103 |

| | | | |

| | | |

| | | |

| 00002000 – 00002FFF | পৃষ্ঠা ২ | 8,192 - 12,288 |

| 00001000 – 00001FFF | পৃষ্ঠা 1 | ৪,০৯৬ – ৮,১৯১ |

| 00000000 – 00000FFF | পৃষ্ঠা 0 | 0 - 4,095 |

একটি অ্যাপ্লিকেশন আজ একাধিক প্রোগ্রাম নিয়ে গঠিত। একটি প্রোগ্রাম একটি পৃষ্ঠার কম সময় নিতে পারে (4096 এর কম) বা এটি দুই বা তার বেশি পৃষ্ঠা নিতে পারে। সুতরাং, একটি অ্যাপ্লিকেশন এক বা একাধিক পৃষ্ঠা নিতে পারে যেখানে প্রতিটি পৃষ্ঠা 4096 বাইট দীর্ঘ। বিভিন্ন ব্যক্তি একটি আবেদন লিখতে পারেন, প্রতিটি ব্যক্তিকে এক বা একাধিক পৃষ্ঠায় বরাদ্দ করা হয়েছে।

লক্ষ্য করুন যে পৃষ্ঠা 0 00000000H থেকে 00000FFF

পৃষ্ঠা 1 00001000H থেকে 00001FFFH, পৃষ্ঠা 2 00002000 থেকে এইচ - 00002FFF এইচ , এবং তাই। একটি 32-বিট কম্পিউটারের জন্য, ফিজিক্যাল পেজ অ্যাড্রেসিংয়ের জন্য প্রসেসরে দুটি 32-বিট রেজিস্টার রয়েছে: একটি বেস অ্যাড্রেসের জন্য এবং অন্যটি ইনডেক্স অ্যাড্রেসের জন্য। পৃষ্ঠা 2 এর বাইট অবস্থানগুলি অ্যাক্সেস করতে, উদাহরণস্বরূপ, বেস ঠিকানার জন্য রেজিস্টার 00002 হওয়া উচিত এইচ যা পৃষ্ঠা 2 প্রারম্ভিক ঠিকানাগুলির জন্য প্রথম 20 বিট (বাম থেকে)। বাকি বিটগুলো 000 এর মধ্যে এইচ এফএফএফ এর কাছে এইচ 'ইনডেক্স রেজিস্টার' নামক রেজিস্টারে আছে। সুতরাং, পৃষ্ঠার সমস্ত বাইট 000 থেকে ইনডেক্স রেজিস্টারে সামগ্রী বৃদ্ধি করে অ্যাক্সেস করা যেতে পারে এইচ এফএফএফ এর কাছে এইচ . ইনডেক্স রেজিস্টারের বিষয়বস্তুর সাথে যুক্ত করা হয় যা কার্যকর ঠিকানা পাওয়ার জন্য বেস রেজিস্টারে পরিবর্তন হয় না। এই ইনডেক্স অ্যাড্রেসিং স্কিম অন্যান্য পৃষ্ঠাগুলির জন্য সত্য।

যাইহোক, প্রতিটি পৃষ্ঠার জন্য অ্যাসেম্বলি ল্যাঙ্গুয়েজ প্রোগ্রামটি কীভাবে লেখা হয় তা সত্যিই নয়। প্রতিটি পৃষ্ঠার জন্য, প্রোগ্রামার 000 পৃষ্ঠা থেকে শুরু করে কোড লেখে এইচ পৃষ্ঠা FFF এইচ . যেহেতু বিভিন্ন পৃষ্ঠার কোড সংযুক্ত থাকে, তাই কম্পাইলার বিভিন্ন পৃষ্ঠায় সমস্ত সম্পর্কিত ঠিকানা সংযুক্ত করতে সূচক ঠিকানা ব্যবহার করে। উদাহরণস্বরূপ, ধরে নিচ্ছি যে পৃষ্ঠা 0, পৃষ্ঠা 1 এবং পৃষ্ঠা 2 একটি অ্যাপ্লিকেশনের জন্য এবং প্রতিটিতে 555 রয়েছে এইচ যে ঠিকানাটি একে অপরের সাথে সংযুক্ত, কম্পাইলার এমনভাবে কম্পাইল করে যে যখন 555 এইচ পৃষ্ঠা 0 এর 00000 অ্যাক্সেস করতে হবে এইচ বেস রেজিস্টারে থাকবে এবং 555 এইচ ইনডেক্স রেজিস্টারে থাকবে। যখন 555 এইচ পৃষ্ঠা 1 এর 00001 অ্যাক্সেস করতে হবে এইচ বেস রেজিস্টারে থাকবে এবং 555 এইচ ইনডেক্স রেজিস্টারে থাকবে। যখন 555 এইচ পৃষ্ঠা 2 অ্যাক্সেস করতে হবে, 00002 এইচ বেস রেজিস্টারে থাকবে এবং 555H সূচক রেজিস্টারে থাকবে। এটি সম্ভব কারণ ঠিকানাগুলি লেবেল (ভেরিয়েবল) ব্যবহার করে সনাক্ত করা যেতে পারে। বিভিন্ন প্রোগ্রামারকে বিভিন্ন সংযোগকারী ঠিকানার জন্য ব্যবহার করা লেবেলের নামের উপর একমত হতে হবে।

পৃষ্ঠা ভার্চুয়াল মেমরি

পেজিং, পূর্বে বর্ণিত হিসাবে, মেমরির আকার বাড়ানোর জন্য একটি কৌশলে পরিবর্তন করা যেতে পারে যাকে 'পৃষ্ঠা ভার্চুয়াল মেমরি' বলা হয়। পূর্বে বর্ণিত সমস্ত শারীরিক মেমরি পৃষ্ঠাগুলিতে কিছু (নির্দেশ এবং ডেটা) আছে বলে ধরে নেওয়া হচ্ছে, সমস্ত পৃষ্ঠা বর্তমানে সক্রিয় নয়। যে পৃষ্ঠাগুলি বর্তমানে সক্রিয় নয় সেগুলি হার্ড ডিস্কে পাঠানো হয় এবং হার্ড ডিস্কের পৃষ্ঠাগুলি দ্বারা প্রতিস্থাপিত হয় যা চলমান হওয়া দরকার। এইভাবে, স্মৃতির আকার বৃদ্ধি পায়। কম্পিউটার চলতে চলতে, নিষ্ক্রিয় হয়ে যাওয়া পৃষ্ঠাগুলি হার্ড ডিস্কের পৃষ্ঠাগুলির সাথে অদলবদল করা হয় যা এখনও সেই পৃষ্ঠাগুলি হতে পারে যা মেমরি থেকে ডিস্কে পাঠানো হয়েছিল। এই সব মেমরি ম্যানেজমেন্ট ইউনিট (MMU) দ্বারা করা হয়.

6.11 সমস্যা

পাঠককে পরবর্তী অধ্যায়ে যাওয়ার আগে একটি অধ্যায়ে সমস্ত সমস্যা সমাধান করার পরামর্শ দেওয়া হচ্ছে।

1) CISC এবং RISC কম্পিউটার আর্কিটেকচারের মিল এবং পার্থক্য দাও। একটি SISC এবং RISC কম্পিউটারের একটি করে উদাহরণ দিন।

2) ক) বিটগুলির পরিপ্রেক্ষিতে CISC কম্পিউটারের নিম্নলিখিত নামগুলি কী: বাইট, ওয়ার্ড, ডাবলওয়ার্ড, কোয়াডওয়ার্ড এবং ডবল কোয়াডওয়ার্ড।

খ) বিটগুলির পরিপ্রেক্ষিতে RISC কম্পিউটারের নিম্নলিখিত নামগুলি কী: বাইট, হাফওয়ার্ড, ওয়ার্ড এবং ডাবলওয়ার্ড।

গ) হ্যাঁ বা না। সিআইএসসি এবং আরআইএসসি উভয় আর্কিটেকচারেই কি ডাবলওয়ার্ড এবং কোয়াডওয়ার্ড একই জিনিস বোঝায়?

3 ক) x64-এর জন্য, সমাবেশ ভাষার নির্দেশাবলীর জন্য বাইটের সংখ্যা কী থেকে কী পর্যন্ত?

খ) ARM 64-এর জন্য সমস্ত সমাবেশ ভাষার নির্দেশাবলীর জন্য বাইটের সংখ্যা কি নির্দিষ্ট? যদি হ্যাঁ, সমস্ত নির্দেশের জন্য বাইটের সংখ্যা কত?

4) x64 এবং তাদের অর্থের জন্য সর্বাধিক ব্যবহৃত সমাবেশ ভাষার নির্দেশাবলী তালিকাভুক্ত করুন।

5) ARM 64 এবং তাদের অর্থের জন্য সর্বাধিক ব্যবহৃত সমাবেশ ভাষার নির্দেশাবলী তালিকাভুক্ত করুন।

6) পুরানো কম্পিউটার হার্ভার্ড আর্কিটেকচারের একটি লেবেলযুক্ত ব্লক ডায়াগ্রাম আঁকুন। আধুনিক কম্পিউটারের ক্যাশে কীভাবে এর নির্দেশাবলী এবং ডেটা বৈশিষ্ট্যগুলি ব্যবহার করা হয় তা ব্যাখ্যা করুন।

7) একটি প্রক্রিয়া এবং একটি থ্রেডের মধ্যে পার্থক্য করুন এবং বেশিরভাগ কম্পিউটার সিস্টেমে প্রক্রিয়া এবং থ্রেড পরিচালনা করে এমন প্রক্রিয়াটির নাম দিন।

8) মাল্টিপ্রসেসিং কি তা সংক্ষেপে ব্যাখ্যা কর।

9) ক) x86 386 µP কম্পিউটার আর্কিটেকচারে প্রযোজ্য পেজিং ব্যাখ্যা করুন।

খ) সম্পূর্ণ মেমরির আকার বাড়ানোর জন্য কীভাবে এই পেজিং পরিবর্তন করা যেতে পারে?